CERN-2015-003 15 June 2015

# ORGANISATION EUROPÉENNE POUR LA RECHERCHE NUCLÉAIRE **CERN** EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH

**Power Converters**

Baden, Switzerland 7–14 May 2014

Proceedings

Editor: R. Bailey

ISBN 978-92-9083-414-4 (paperback) ISBN 978-92-9083-415-1 (PDF) ISSN 0007-8328 DOI http://dx.doi.org/10.5170/CERN-2015-003

Available online at https://cds.cern.ch/

Copyright © CERN, 2015

Creative Commons Attribution 4.0

Knowledge transfer is an integral part of CERN's mission.

This CERN Yellow Report is published in Open Access under the Creative Commons Attribution 4.0 license (http://creativecommons.org/licenses/by/4.0/) in order to permit its wide dissemination and use. The submission of a contribution to a CERN Yellow Report shall be deemed to constitute the contributor's agreement to this copyright and license statement. Contributors are requested to obtain any clearances that may be necessary for this purpose.

This report is indexed in: CERN Document Server (CDS), INSPIRE, Scopus.

This report should be cited as:

Proceedings of the CAS–CERN Accelerator School: Power Converters, Baden, Switzerland, 7–14 May 2014, edited by R. Bailey, CERN-2015-003 (CERN, Geneva, 2015), http://dx.doi.org/10.5170/CERN-2015-003

A contribution in this report should be cited as:

[Author name(s)], in Proceedings of the CAS–CERN Accelerator School: Power Converters, Baden, Switzerland, 7–14 May 2014, edited by R. Bailey, CERN–2015–003 (CERN, Geneva, 2015), pp. [first page] – [lastpage], http://dx.doi.org/10.5170/CERN-2015-003. [first page]

## Abstract

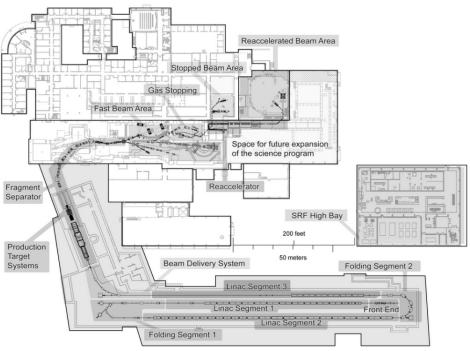

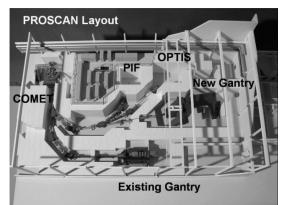

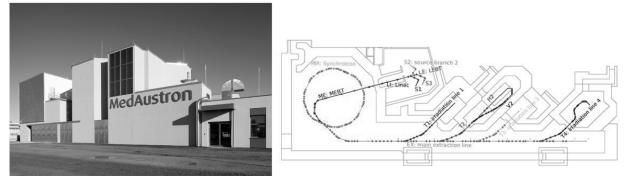

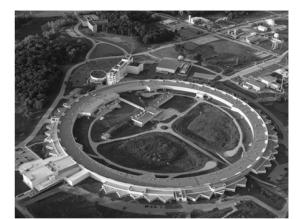

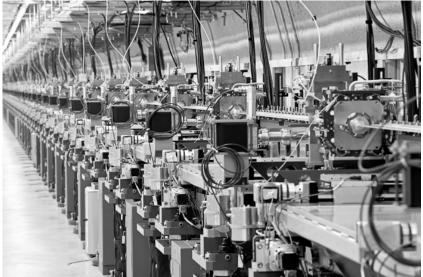

These proceedings collate lectures given at the twenty-eighth specialized course organised by the CERN Accelerator School (CAS). The course was held at the Hotel du Parc, Baden, Switzerland from 7 - 14 May 2014, in collaboration with the Paul Scherrer Institute. Following introductory lectures on accelerators and the requirements on power converters, the course covered components and topologies of the different types of power converters needed for particle accelerators. Issues of design, control and exploitation in a sometimes-hostile environment were addressed. Site visits to ABB and PSI provided an insight into state-of-the-art power converter production and operation, while topical seminars completed the programme.

## Preface

The aim of the CERN Accelerator School (CAS) is to collect, preserve and disseminate the knowledge accumulated in the world's accelerator laboratories over the years. This applies not only to general accelerator physics, but also to related sub-systems and associated technologies, and to how these are adapted to particular requirements. This wider aim is achieved by means of specialized courses currently held yearly. The topic of the 2014 specialized course was Power Converters and was held at the Hotel du Parc, Baden, Switzerland from 7 to 14 May 2014.

The course was made possible through the fruitful collaboration with the Paul Scherrer Institute in Villigen, Switzerland, in particular through the efforts of Lenny Rivkin, René Künzi, Marlen Bugmann and Daniela Lerch.

The backing of the CERN management and the guidance of the CAS Advisory and Programme Committees enabled the course to take place, while the attention to detail of the Local Organising Committee and the management and staff of the Hotel du Parc ensured that the school was held under optimum conditions.

Financial support offered by OCEM, Italy and CAENels, Slovenia allowed scholarships to be offered to deserving students who would not otherwise have been able to attend, while both PSI in Villigen and ABB in Turgi hosted extremely interesting half-day visits. There was also a small industrial exhibition featuring OCEM, CAELels, Hivolt and Ampegon.

Special thanks must go to the lecturers for the preparation and presentation of the lectures, even more so to those who have written a manuscript for these proceedings.

The enthusiasm of the 84 participants of 21 nationalities, from institutes in 14 countries, provides convincing proof of the usefulness and success of the course.

For the production of the proceedings we are indebted to the efforts of Barbara Strasser and to the CERN E-Publishing Service, especially Valeria Brancolini for her very positive and efficient collaboration.

These proceedings have been published in paper (black and white) and electronic form. The electronic version, with full colour figures, can be found at https://cds.cern.ch/collection/CERN%20Yellow%20Reports.

Roger Bailey CERN Accelerator School

| 08:30<br>09:30<br>09:30 |               | 8 May                                   | 9 May                                       | 10 May                                                        | 11 May            | I2 May                                                                            | 13 May            | w eun estay<br>14 May       |

|-------------------------|---------------|-----------------------------------------|---------------------------------------------|---------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------|-------------------|-----------------------------|

| 09:30<br>09:30          |               | Introduction and<br>Accelerator Basics  | Power Converters and<br>Power Quality<br>I  | RF Solid State<br>Amplifiers                                  |                   | Thermal Design                                                                    |                   | Simulations                 |

| 09:30                   |               | R. Bailey                               | K. Kahle                                    | J. Jacob                                                      |                   | R. Kuenzi                                                                         |                   | N. Ngada                    |

|                         |               | Requirements on                         | EMC                                         | Long Pulse                                                    |                   | Design Methods and                                                                |                   | Power                       |

|                         |               | Power                                   |                                             | Converters                                                    |                   | Tools                                                                             |                   | Converters for              |

|                         | V             | Converters                              |                                             |                                                               |                   |                                                                                   |                   | Accelerators                |

| 10:30                   | R             | JP. Bumet                               | A. Charoy                                   | J. Eckoldt                                                    | E                 | T. Meynard                                                                        |                   | R. Visintini                |

|                         |               | COFFEE                                  | COFFEE                                      | COFFEE                                                        |                   | COFFEE                                                                            |                   | COFFEE                      |

| 11:00                   | х –           | Definition of Power<br>Converters<br>I  | Power Converters and<br>Power Quality<br>II | Solid State Power<br>Modulators                               | C X               | Regulation<br>Theory                                                              | Half<br>Day<br>at | Putting It Into<br>Practice |

| 12:00                   | ٧             | D. Aguglia                              | D. Siemaszko                                | J. Biela                                                      | Ŋ                 | F. Bouvet                                                                         |                   | JP. Burnet                  |

| 12:00                   | V I           | Definition of Power<br>Converters<br>II | Switched Mode<br>1 Q Converters             | Power Converter<br>Controls: Radiation<br>Risks & Mitigations | <b>צ</b> 2        | High Precision Current<br>Measurement for Power<br>Converters                     | +                 | Closing Remarks             |

| 13:00                   | 1             | D. Aguglia                              | R. Petrocelli                               | B. Todd                                                       | 2                 | M. Cerqueira                                                                      | Half              | R. Bailey                   |

|                         |               | LUNCH                                   | LUNCH                                       | LUNCH                                                         | I                 | LUNCH                                                                             | Day at            | LUNCH                       |

| 14:30                   | Q V           | Active Devices                          | Switched Mode<br>4 Q Converters             | Power Filter Design                                           | 0 Z               | A Review of ADCs &<br>DACs and their<br>Application                               | ISI               | a 🖻                         |

| 15:30                   |               | M. Rahimo                               | Y. Thurel                                   | R. Kuenzi                                                     |                   | J. Pickering                                                                      |                   | 1                           |

| 15:30                   | >             | Passive Devices<br>Magnetic             | Converters for<br>Low Frequency<br>Machines | Protection and<br>Interlocks                                  |                   | Controls and<br>Interfaces                                                        |                   | A A                         |

| 16:30                   |               | P. Viarouge                             | JF. Bouteille                               | B. Todd                                                       |                   | Q. King                                                                           |                   | R                           |

|                         |               | TEA                                     | TEA                                         | TEA                                                           |                   | TEA                                                                               |                   | E                           |

| 17:00                   |               | Passive Devices<br>Capacitive           | Seminar<br>Proton Therapy                   | Swiss FEL, the X-Ray                                          |                   | Seminar<br>Overview on Latest                                                     |                   | - ;                         |

|                         |               |                                         |                                             | Free Electron Laser at<br>PSI                                 |                   | Development of ABB's<br>Power Semiconductors<br>Technology and<br>Research Topics |                   | ⊃ ≃ ;                       |

| 18:00 H                 | Registration  | R. Gallay                               | G. Goitein                                  | H. Braun                                                      |                   | I. Nistor                                                                         |                   | 2                           |

| 19:00 <b>B</b><br>19:30 | Buffet Dinner | Dinner                                  | Dinner                                      | Dinner                                                        | Special<br>Dinner | Dinner                                                                            | Dinner            |                             |

## Contents

| Preface                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| R. Bailey v                                                                                                                                         |

| Requirements on Power Converters<br>J-P. Burnet                                                                                                     |

| Definition of Power Converters<br><i>F. Bordry and D. Aguglia</i>                                                                                   |

| Metallized Film Capacitor Lifetime Evaluation and Failure Mode Analysis <i>R. Gallay</i> 45                                                         |

| Power Converters and Power Quality<br><i>K. Kahle</i>                                                                                               |

| Electromagnetic Compatibility of Power Converters <i>A. Charoy</i>                                                                                  |

| Double-Frame Current Control with a Multivariable PI Controller and Power Compensation for Weak<br>Unbalanced Networks<br>D. Siemaszko and A. Rufer |

| One-Quadrant Switched-Mode Power Converters<br><i>R. Petrocelli</i>                                                                                 |

| Switched Mode Four-Quadrant Converters<br><i>Y. Thurel</i>                                                                                          |

| Power Converters for Cycling Machines<br>J-F. Bouteille                                                                                             |

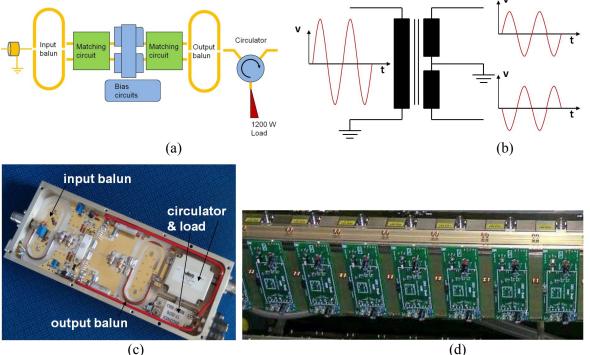

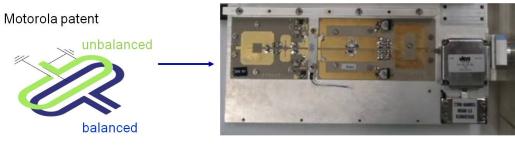

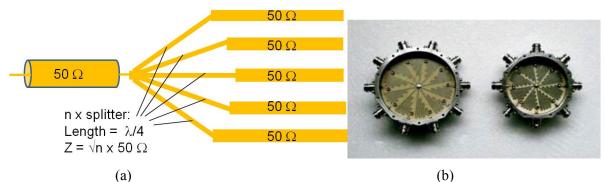

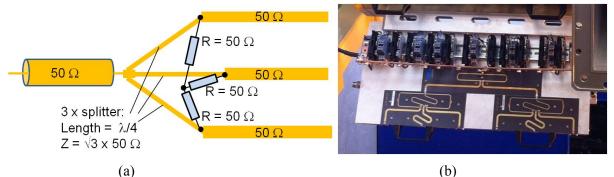

| RF Solid State Amplifiers<br>J. Jacob                                                                                                               |

| Long Pulse Modulators<br>J. Eckoldt                                                                                                                 |

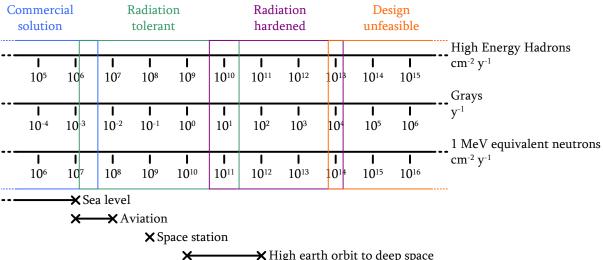

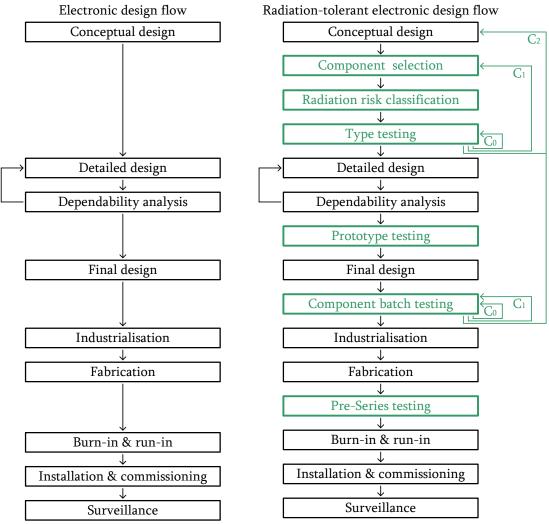

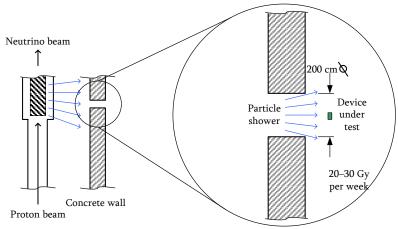

| Radiation Risks and Mitigation in Electronic Systems      B. Todd and S. Uznanski      245                                                          |

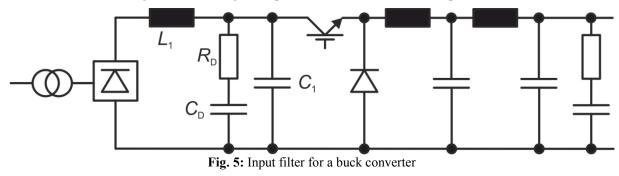

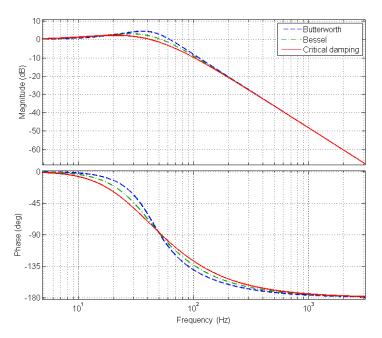

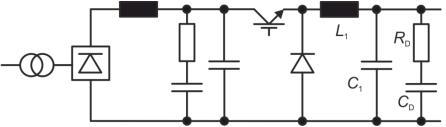

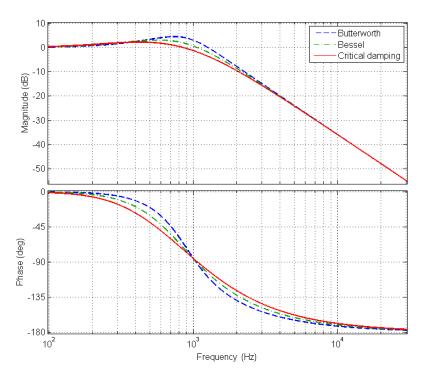

| Passive Power Filters<br><i>R. Künzi</i>                                                                                                            |

| Risk and Machine Protection for Stored Magnetic and Beam Energies<br><i>B. Todd and M. Kwiatkowski</i>                                              |

| Thermal Design of Power Electronic Circuits <i>R. Künzi</i>                                                                                         |

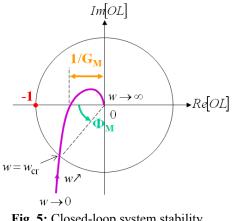

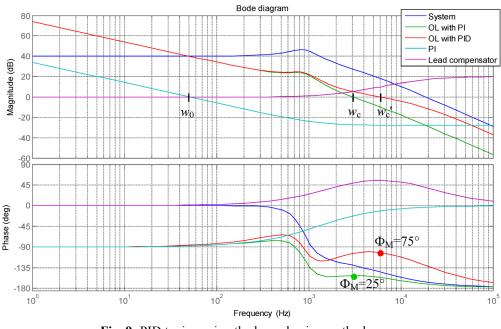

| Regulation Theory <i>F. Bouvet</i>                                                                                                                  |

| High Precision Current Measurement for Power Converters      M. Cerqueira Bastos      353                                                           |

| Analogue to Digital and Digital to Analogue Converters (ADCs and DACs): A Review Update <i>J. Pickering</i>                                         |

| Controls and Interfaces<br>Q. King                                                                                                                  |

| Simulations <i>N.M. Ngada</i>                                                                                                                       |

| Power Converters for Accelerators |     |

|-----------------------------------|-----|

| R. Visintini                      | 415 |

| Putting it into Practice          |     |

| J-P. Burnet                       | 445 |

| List of Participants              | 459 |

## **Requirements for Power Converters**

*J.-P. Burnet* CERN, Geneva, Switzerland

## Abstract

This paper introduces the requirements for power converters needed for particle accelerators. It describes the role of power converters and the challenges and constraints when powering magnets. The different circuit layouts are presented as well as the operating cycles. The power converter control and high precision definition are also introduced. This paper lists the key circuit parameters to be taken into consideration to properly specify a power converter that can be compiled in a functional specification.

## Keywords

Magnet Power supply; power electronics; power converter control.

## 1 Introduction

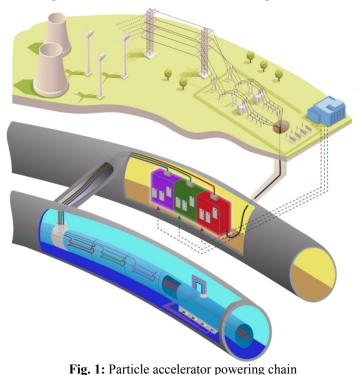

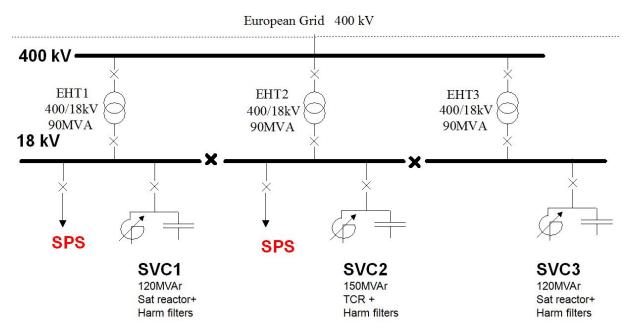

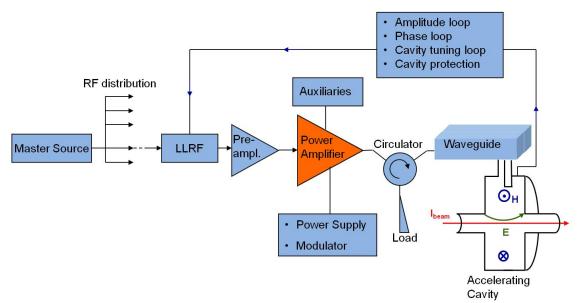

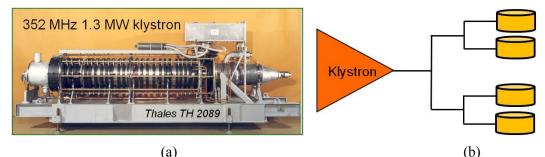

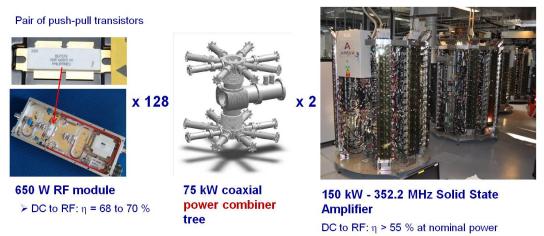

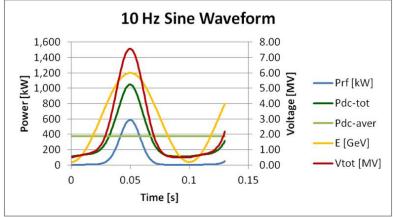

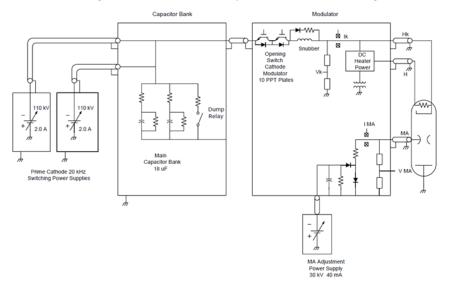

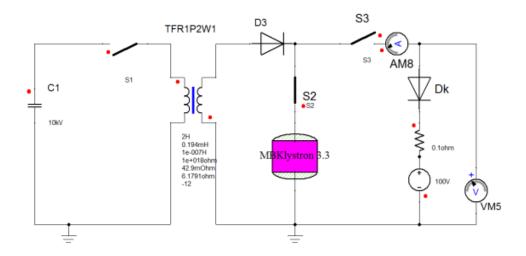

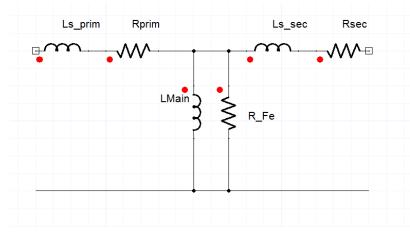

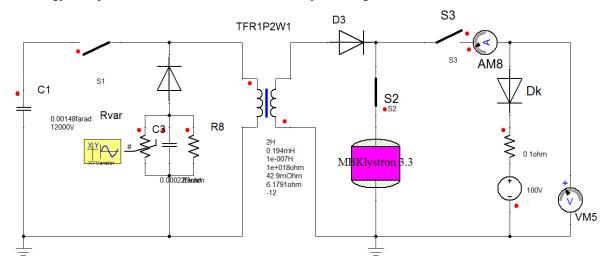

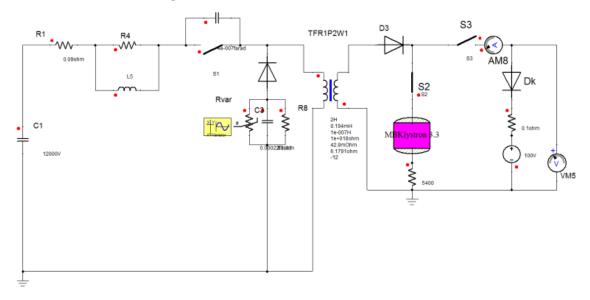

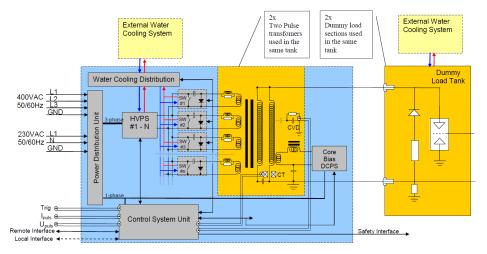

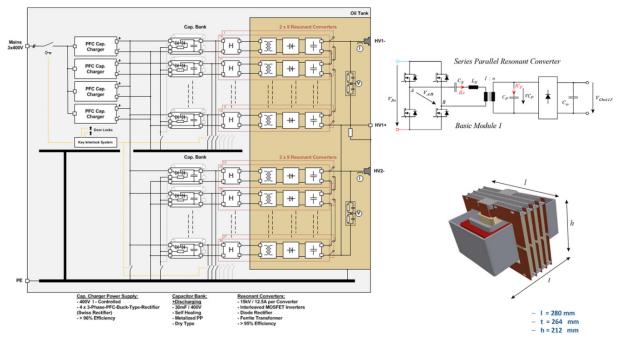

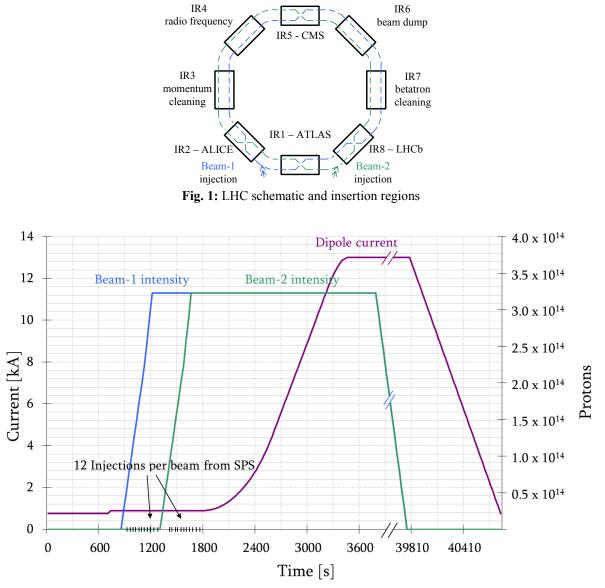

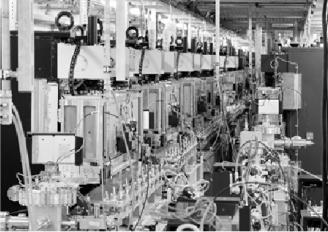

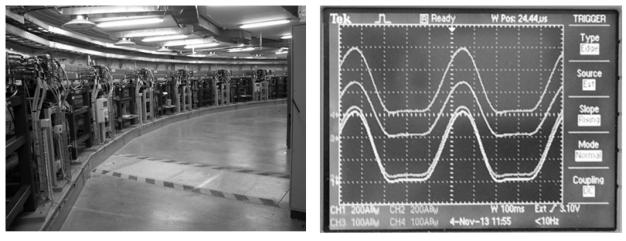

Particle accelerators are very special machines that consume a lot of electricity. The main devices consuming this energy are the magnets and the radio-frequency (RF) systems. It represents from 70% to 90% of the total energy needed for a machine. The way to power these two main loads is always special and needs a lot of care to obtain the right performance from the machine, see Fig. 1. The performance of the power converters directly impacts upon the beam quality, and the requirements for power converters are outside the range of classical industrial products. This paper will introduce the power converters needed for particle accelerators, and their main parameters.

0007-8328 - © CERN, 2015. Published under the Creative Common Attribution CC BY 4.0 Licence. http://dx.doi.org/10.5170/CERN-2015-003.1

#### 2 Type of loads

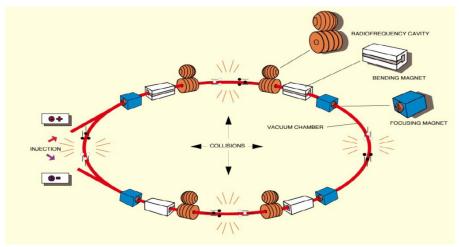

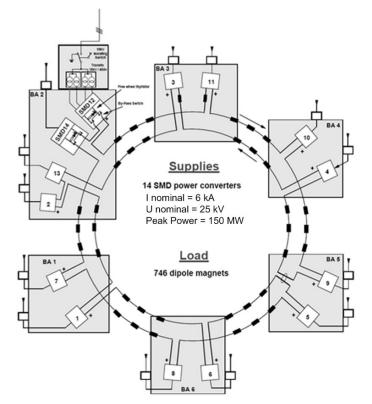

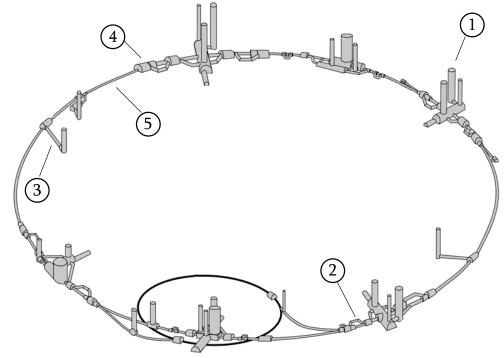

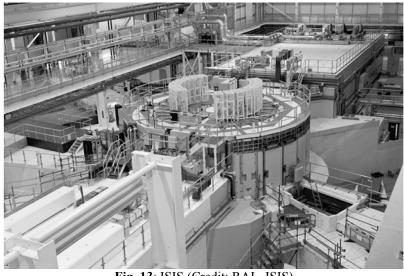

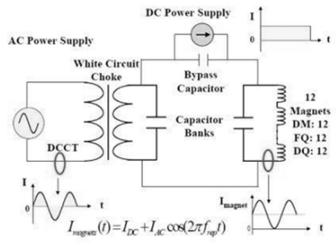

The most popular particle accelerator today is the synchrotron machine. In such machines, a large number of magnets is used to control the beam and, depending of the type of particle, there may be many radio-frequency cavities for acceleration, see Fig. 2. This paper will mainly concentrate upon magnet powering, as radio-frequency powering is covered by another paper.

Fig. 2: Basic concept of a synchrotron machine

The power converters or power supplies are the devices that take energy from the electrical grid and transform it to control the flow of energy supplied to the magnets or radio-frequency power amplifiers. The magnet power converters are always of an AC/DC type.

## **3 Powering magnets**

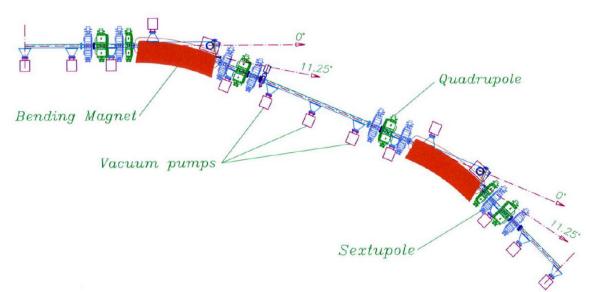

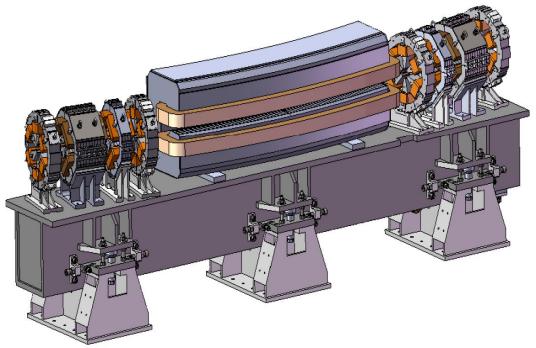

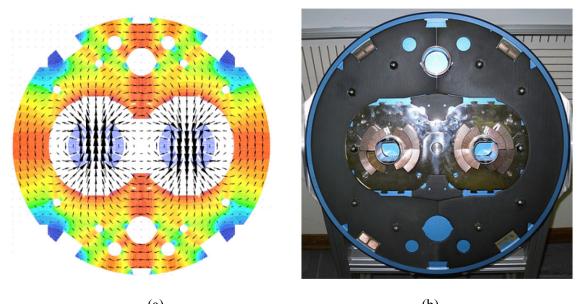

Different types of magnets are needed for particle accelerators, see Fig. 3. The two main families are the dipole magnets that bend the beam and the quadrupole magnets that focus the beam. Sextupole magnets are used to correct the chromaticity, and octupole magnets control the Landau damping. Particle accelerators also need a lot of small correctors to compensate for local distortion due to magnet imperfections, alignment, etc.

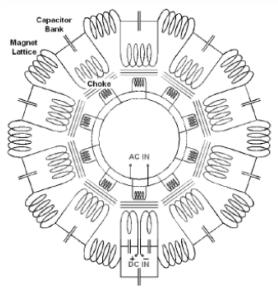

A synchrotron is composed of a periodic repetition of focus-defocus (FODO) cells. Each cell contains dipole, quadrupole and sextupole magnets, see Figs. 4 and 5 [1].

Fig. 3: Different magnet types: (a) dipole magnet; (b) quadrupole magnet; (c) sextupole magnet; (d) octupole magnet.

Fig. 4: Arrangement of the magnets within one unit cell of the SESAME storage ring

Fig. 5: SESAME FODO cell

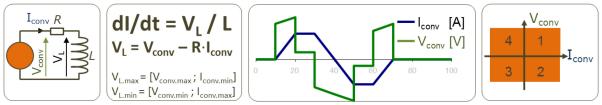

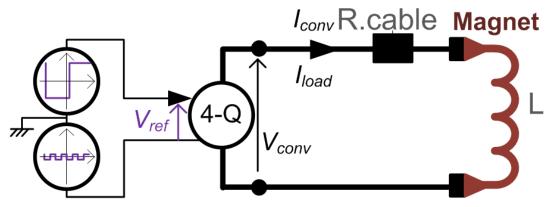

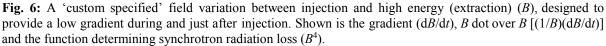

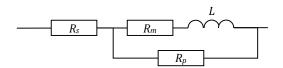

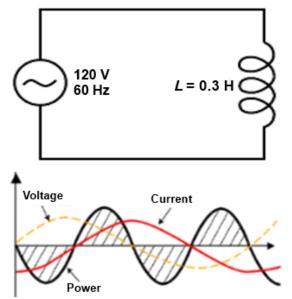

The magnets are made with a magnetic core (laminated or not) and winding coils. As seen by the power converters, the magnets are always inductive loads. The equivalent circuit is an inductance in series with a resistor (due to the resistance of the coils and the DC cables between the power converter and the magnet).

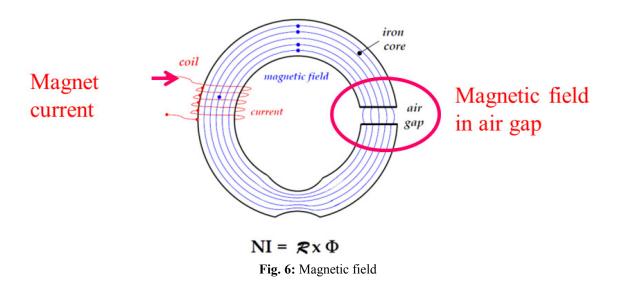

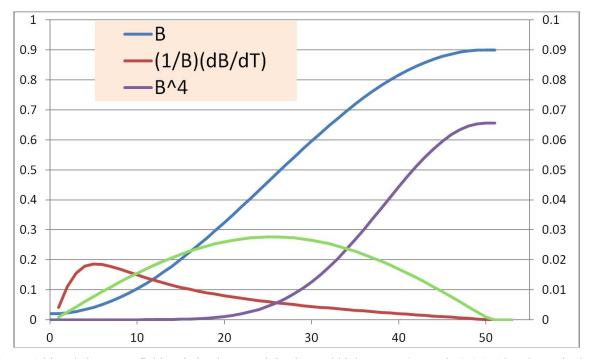

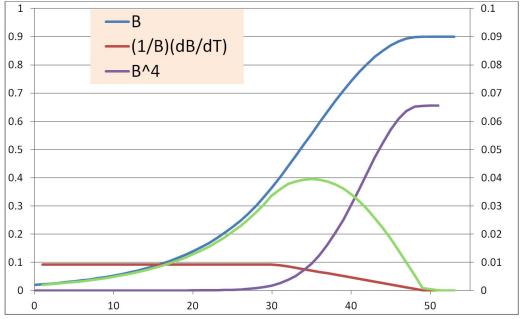

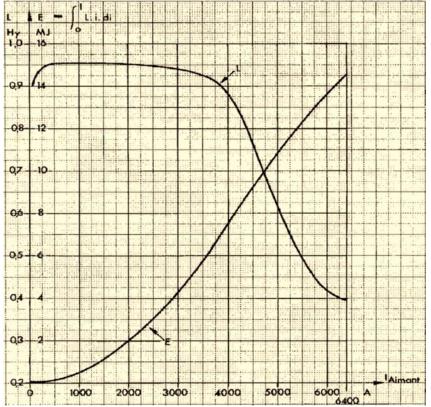

In a synchrotron the beam energy is proportional to the magnetic field of the dipole magnets. The magnetic field is generated by the current circulating in the magnet coils, see Fig. 6. To then control the beam, the operators need to control the current through the magnets.

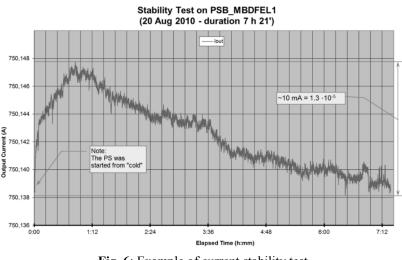

The main specification for the magnet power converters is high precision control of the current delivered to the magnets. Typically, the good field region of a magnet is defined within  $\pm 10^{-4} \Delta B/B$  and the typical performance of the power converter is to control the current to the order of  $10^{-5}$  of the maximum output current.

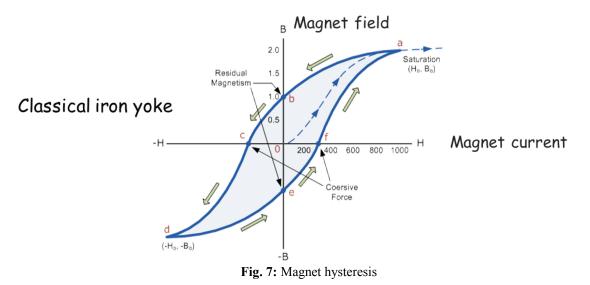

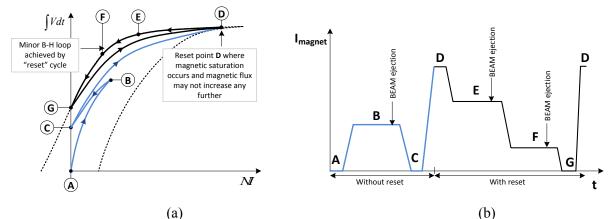

The main difficulty is the fact that in a magnet the relation between the current and magnetic field is not linear due to magnetic hysteresis of the core and the eddy currents, see Fig. 7.

This problem is one of the major difficulties when operating a synchrotron that is to work with different beam energies.

#### 3.1 Magnet parameters

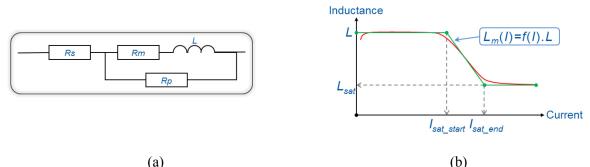

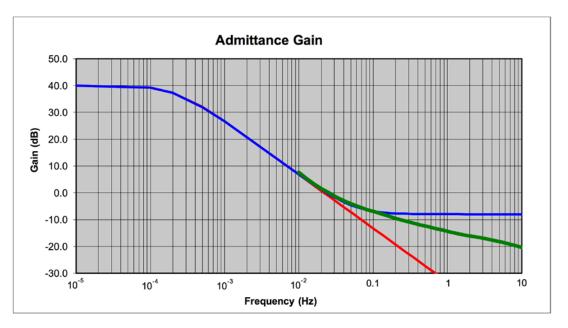

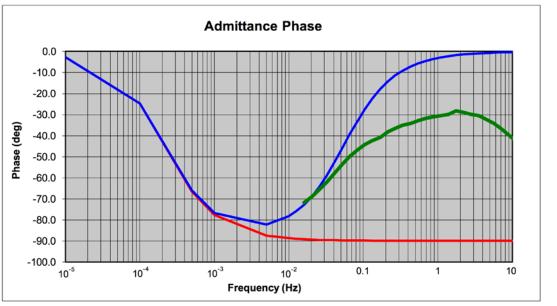

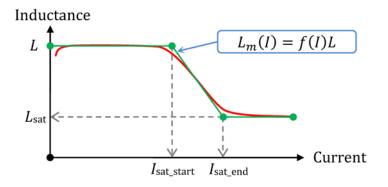

A good model of the load is needed to control the current delivered by the power converters. The transfer function gives the main parameters of the circuit which are inductance and resistance. To improve control, it is mandatory to include the saturation curve of the magnet to adapt the current loop parameters depending of the current level, see Fig. 8(b).

**Fig. 8:** Magnet model: (a) equivalent circuit of the load (b) inductance value versus current

#### 3.2 Circuit layout

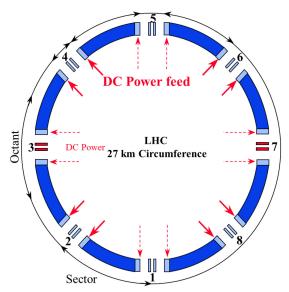

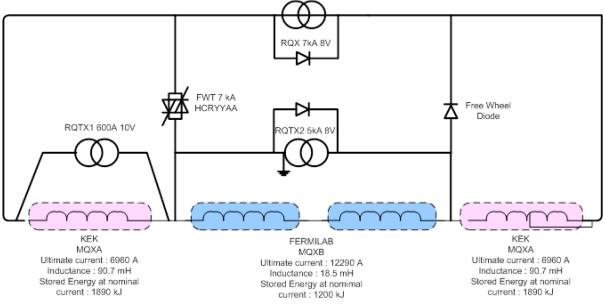

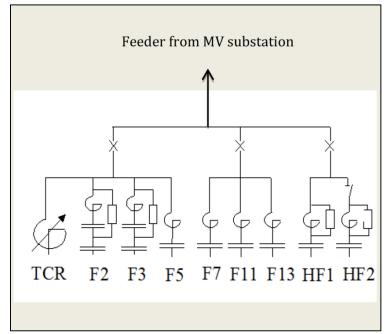

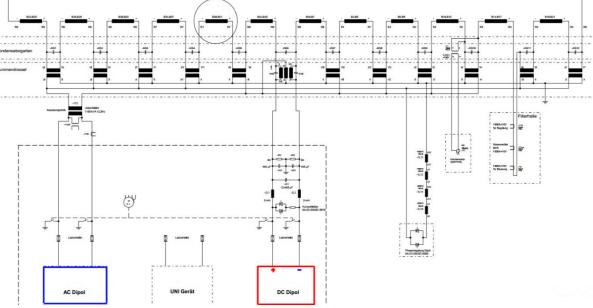

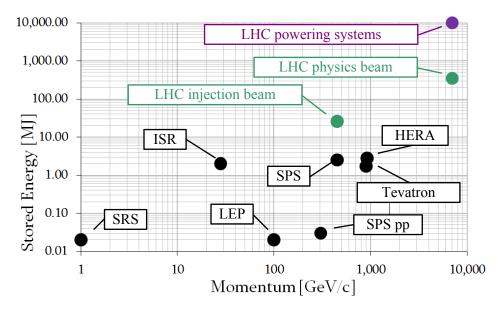

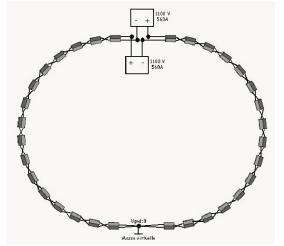

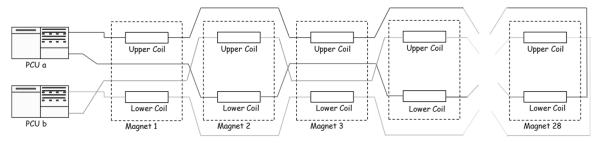

The magnets can be powered individually or in series. The main advantage to powering them individually is the increase in flexibility of the beam optics. The main drawback is the uncertainty of the magnetic field between the magnets due to the magnet current history (hysteresis effect). The global cost is also higher, with more DC cables and more power converters. In some cases it can become mandatory to split a circuit because of the size of the load becoming too large. For example, this is the case for the LHC superconducting dipoles and quadrupoles, where the total energy of the circuit is very huge (8 GJ). The machine was therefore divided into eight sectors, see Fig. 9. Even with this split, the inductance of one octant is 15 H with a stored energy of more than 1 GJ. This configuration needs high-precision control of the magnet current as well as excellent tracking of the magnet current between the eight sectors [2].

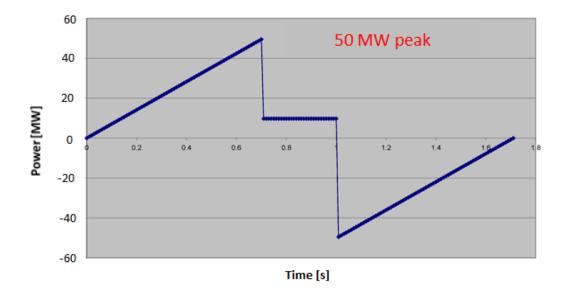

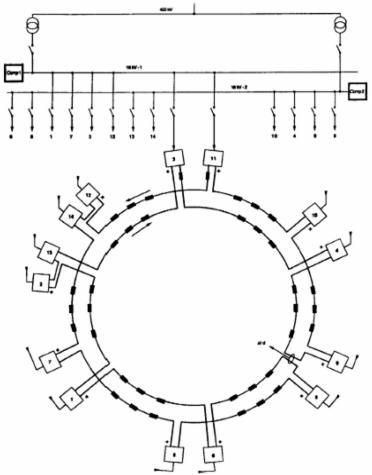

Fig. 9: Split of the LHC dipole and quadrupole circuits

The classical solution for dipole, quadrupole, and sextupole magnets is to connect all of them in series. The main advantage is that this suppresses the uncertainty of the magnetic field between magnets and assures easy control of these circuits. In some cases, trim power converters are needed to adapt the magnetic field locally. This solution is globally the cheapest one, but it requires a large power converter to power such circuits. As an example, the SPS machine requires a power system of 150 MW to power all of the dipole in series. A special distribution of power sources was chosen to reduce the common mode voltage applied to the magnets, see Fig. 10.

In some cases, the creation of nested circuits reduces the cost of the powering system. In a series of magnets that are powered by a main power converter, some magnets have additional connections to a trim power converter to adjust their current, see Fig. 11. This creates some difficulties for the power converter control as the different power converters are coupled by their load. This type of scheme isn't recommended due to the induced complexity. However, in some case the savings are such that it is difficult to avoid this solution [3].

Fig. 10: SPS dipole power system

Fig. 11: LHC inner triplet powering scheme

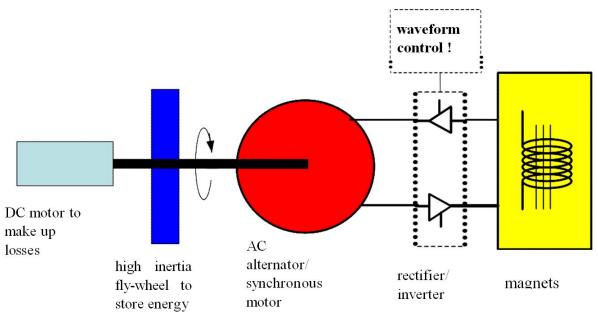

#### 3.3 Powering optimization

Powering optimization plays with the magnet parameters, the power converter parameters, and the circuit layout. For the same integral magnetic field, the magnet can be laid out in different ways. The magnet parameters are the number of turns per coil, the maximum current, the current density in the conductor, and the length of the magnet [4].

The number of turns per coil does not influence the total power losses in the magnet. By increasing the number of turns, the current required decreases linearly. This reduces the losses in the DC cables and power converters. The drawback is the higher voltage applied to the magnets and the increased size of the magnet due to insulation.

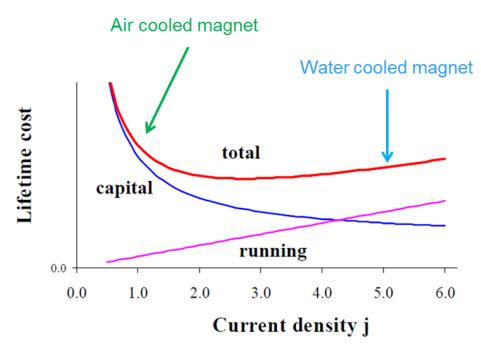

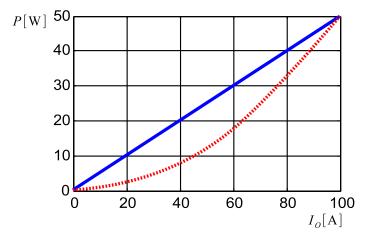

The magnet's current density determines the magnet's losses. The choice is made based on economic criteria. High current densities result in a small conductor cross-section, but with water cooling. This reduces the size of the magnet and thus the capital costs, but it requires larger power converters and gives increased running costs due to the magnet's losses. By lowering the current density, the electricity bills can be strongly reduced but at the price of having to invest in larger magnets, as shown in Fig. 12. A global optimization has to be carried out to find the best economical solution for the magnets as well as for the power converters.

Fig. 12: The variation in magnet capital cost, running cost, and total lifetime cost versus conductor current density.

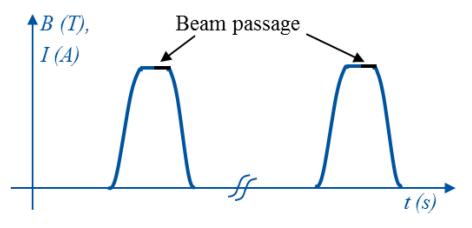

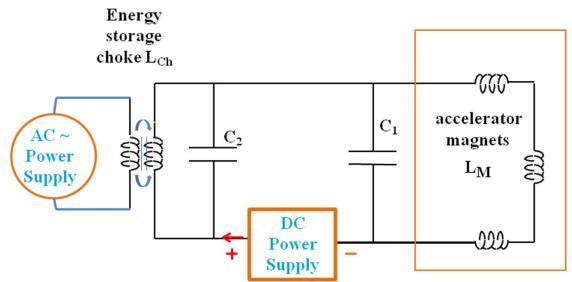

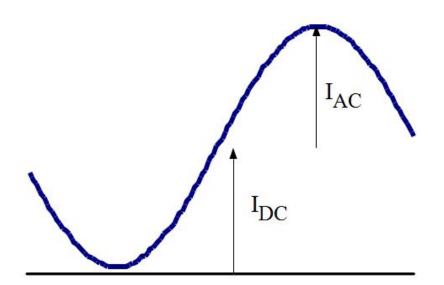

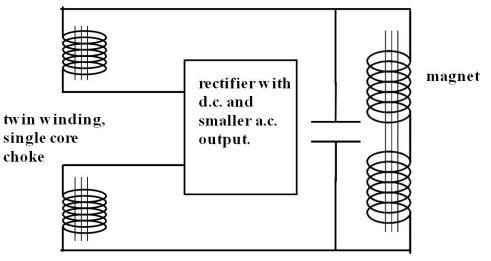

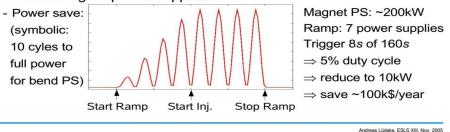

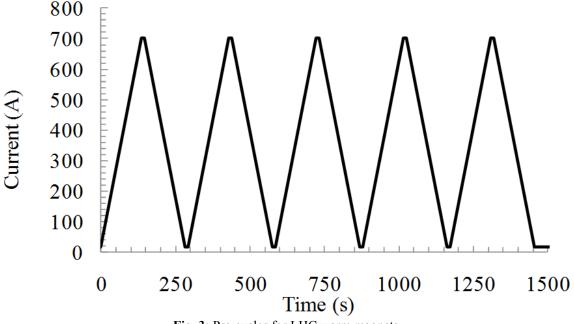

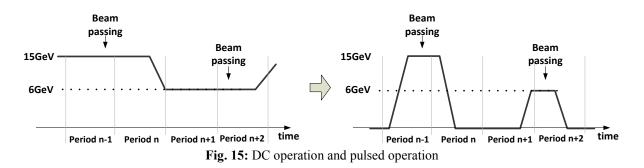

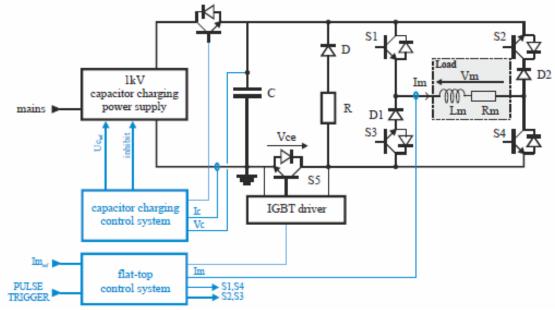

Another way to reduce power consumption is to reduce the time during which the magnets are powered. This is, for example, the case for linacs and transfer lines where the beam isn't always present, see Fig. 13. The idea is to power the magnets only when the beam is present, and this has a strong impact on electricity consumption. For example, in Linac4, the beam is pulsing at 2 Hz while the beam is present for 2 ms. The duty is then 0.4%. By pulsing the magnets, when compared to DC magnets, the savings are enormous (99%). This technique requires special designs for those power converters where energy storage can be implemented.

Fig. 13: Beam passage versus time

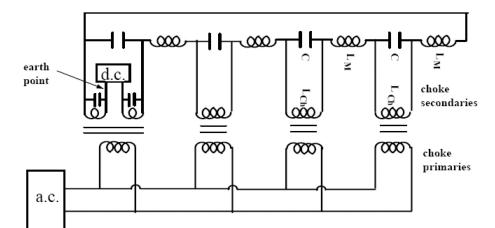

## 3.4 Magnet grounding

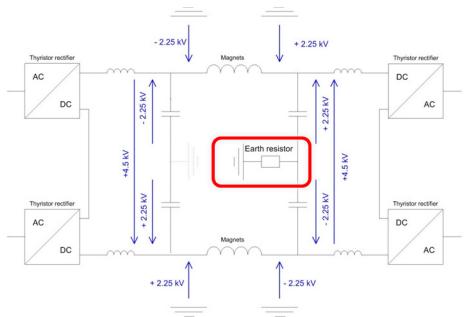

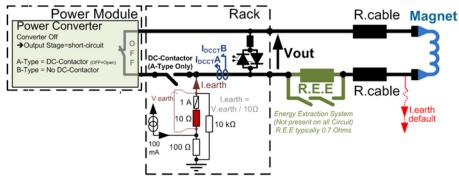

For safety reasons, magnets are isolated from the electrical grid. The power converter needs an isolation transformer in its topology. Magnets are connected to the ground at one point; they can't be left floating with their parasitic capacitances. One polarity can be connected directly to the ground through a resistor to limit the earth fault current, or via a divider for better voltage sharing, see Fig. 14. The ground current is monitored and stops the power converter in the case of an earth fault in the DC circuit.

Fig. 14: An example of earthing the system

For a large number of magnets in series, the arrangement of multiple power sources can be made so that the common mode voltage of the magnets (any polarity of the magnet to ground) is reduced, when compared to the total applied voltage in differential mode. As shown in Fig. 14, the total applied voltage is 9 kV while the maximum common voltage of the magnets is limited to 2.25 kV.

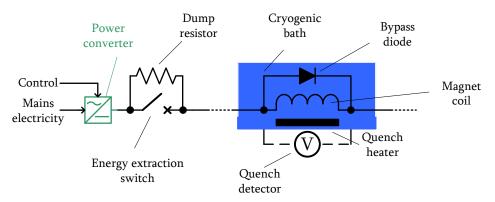

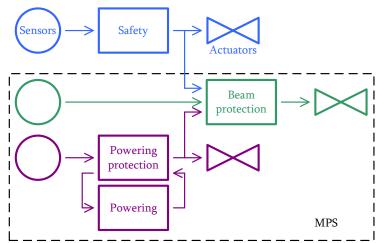

## 3.5 Magnet protection

The magnets will have an interlock system that requests the power converter to stop in the event of any faults. For warm magnets, it is quite simple (water flow, thermostat, red button, etc.) For superconducting magnets, it is quite complex (quench protection, cryogenics, etc.)

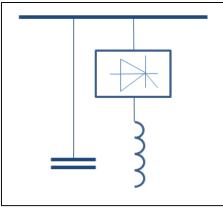

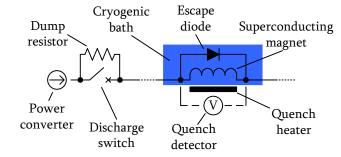

In the event of a fault, the magnet current will be stopped but, because the magnets are inductive loads, the circuit can't be opened. The power converters assure a freewheeling path to the current, and the decay time is determined by the time constant of the circuit (L, R). In some cases, an additional dump resistor is needed to accelerate the discharge time, see Fig. 15.

Fig. 15: Output circuit for magnet protection

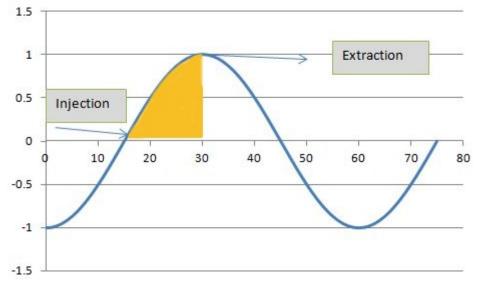

## 3.6 Operation cycle

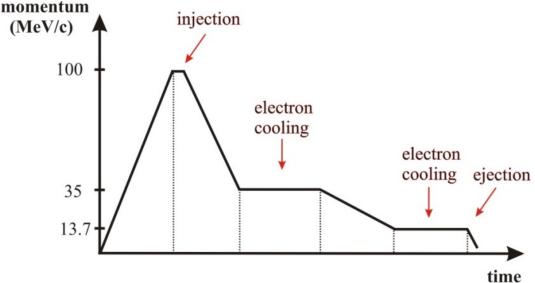

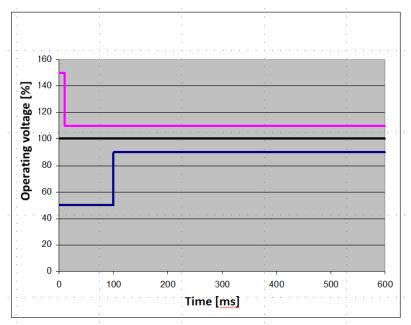

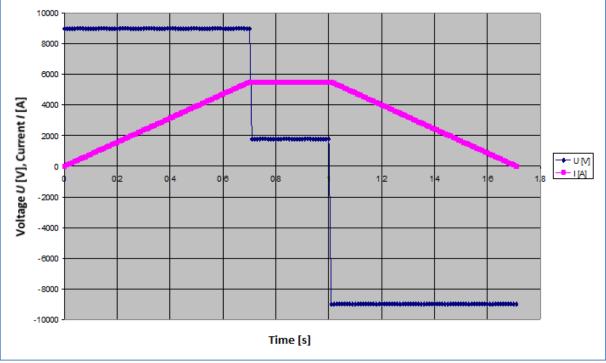

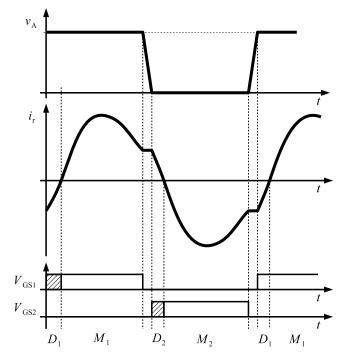

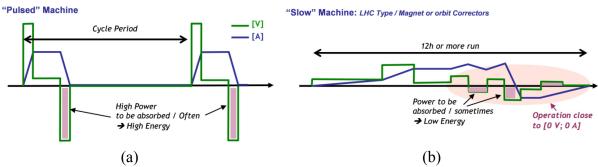

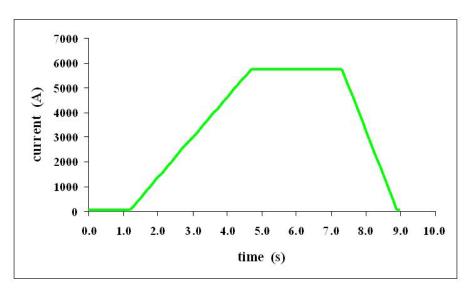

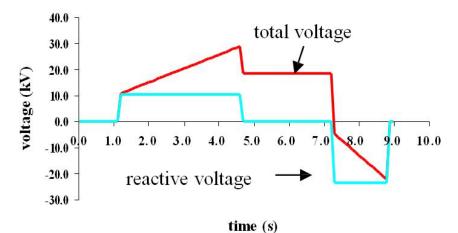

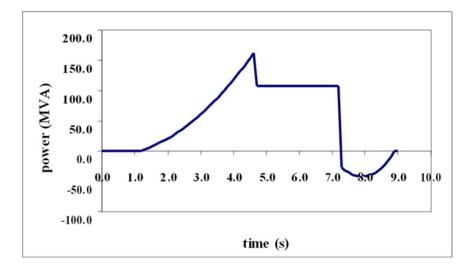

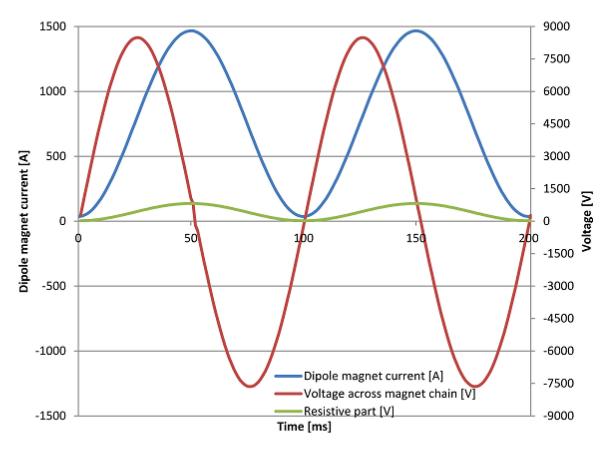

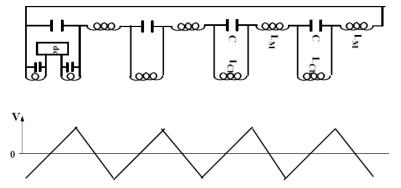

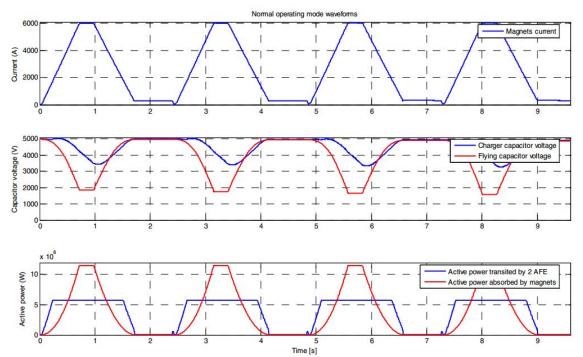

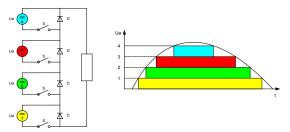

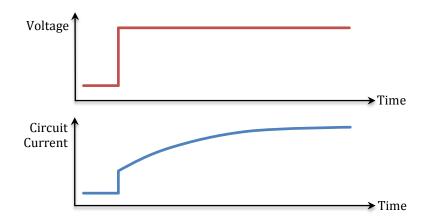

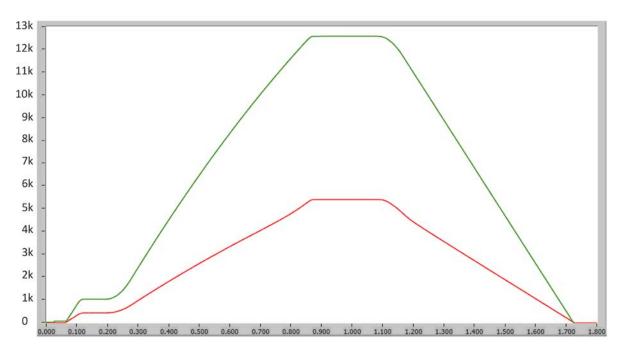

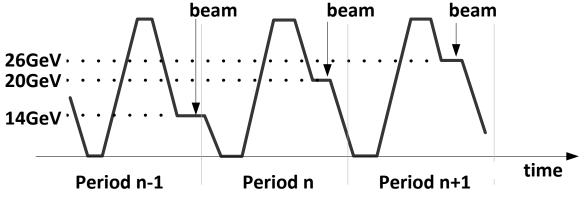

Magnet operation has a strong impact on the power converter topology and on power converter ratings. The magnet current cycle has to be defined from the beginning of a project, see Fig. 16.

Fig. 16: An example of the ELENA operating cycle

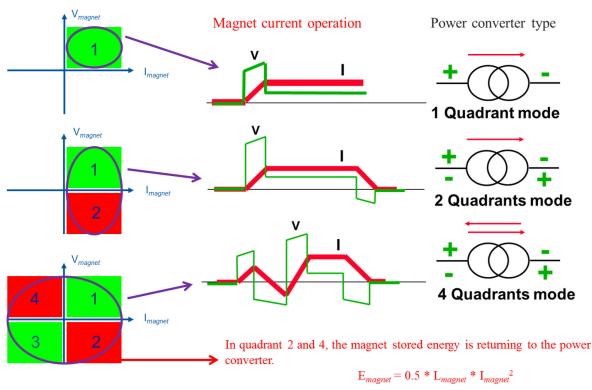

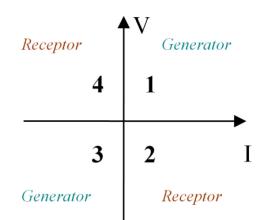

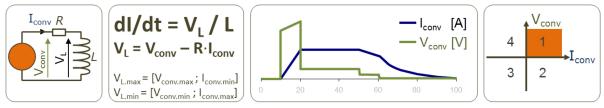

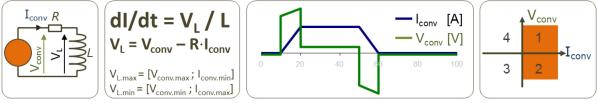

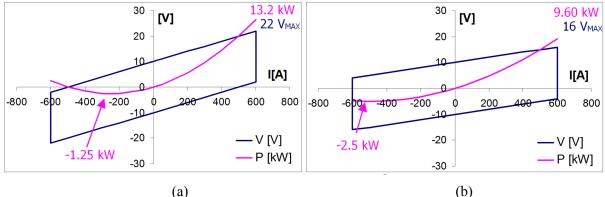

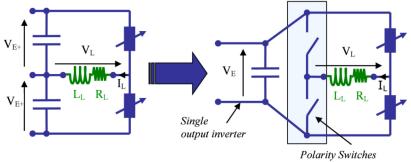

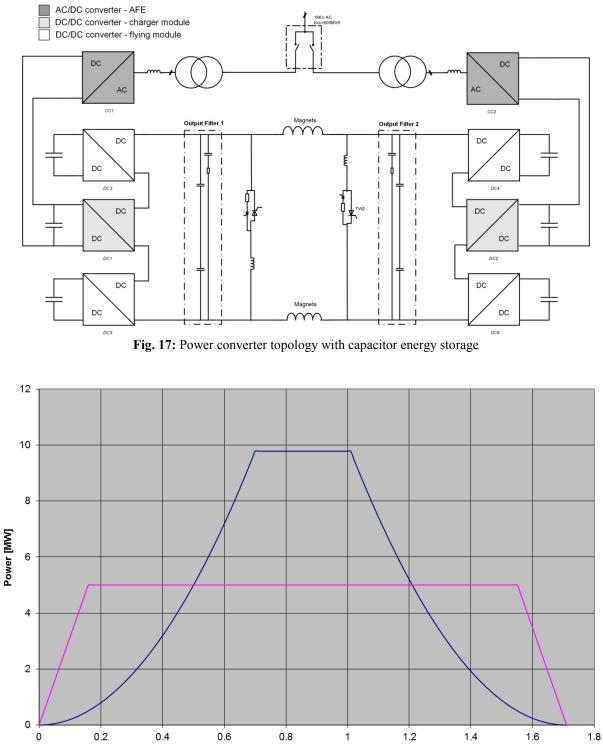

The main parameters to be defined are the minimum and maximum operating current and the ramp rates. This will define the voltage needed and the topology of the converters. If the applied current and voltage are always positive, then a one-quadrant converter can be selected. If the current is always positive but the voltage is bipolar, then the power converter must be of the two-quadrant type. If the voltage and the current are bipolar, then, a four-quadrant power converter will be required, see Fig. 17.

Fig. 17: The power converter type depends upon the operating cycle

## 4 **Power converters**

The power converter types will be introduced in the following papers. Control of power converter current is a challenge, and the main principles are described below.

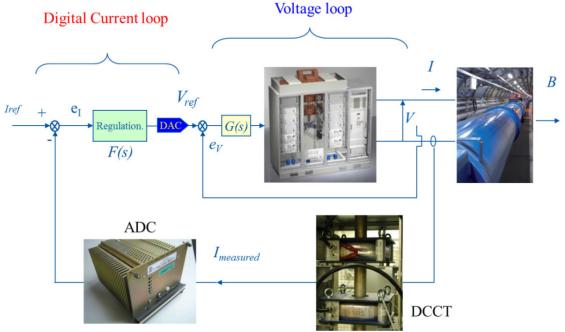

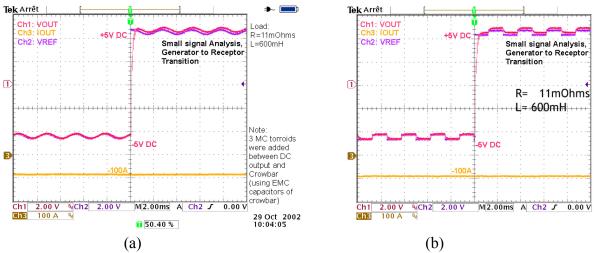

## 4.1 **Power converter control**

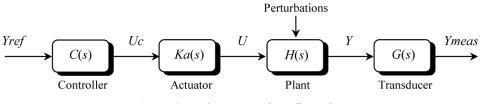

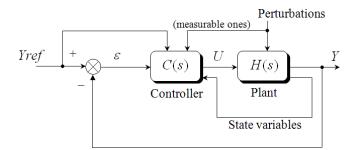

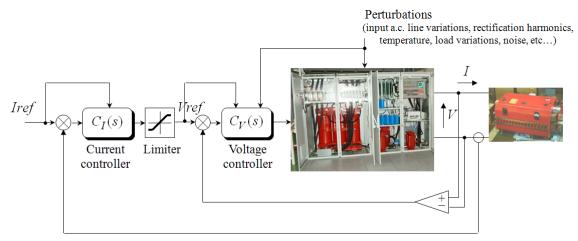

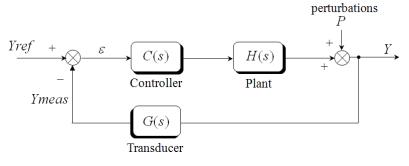

Power converter performance has to be defined at the beginning of the project, based on the accelerator's requirements. The power converters needed for particle accelerators are always of highclass precision. The term 'precision' is only a generic term covering accuracy, reproducibility, and stability. For each power converter, the requirements depend on the magnet type and function. The most demanding are the dipole and quadrupole magnets, typically in the order of  $1-10 \times 10^{-5}$ , while the performance for corrector magnets are less demanding, typically in the order of  $1-10 \times 10^{-4}$ .

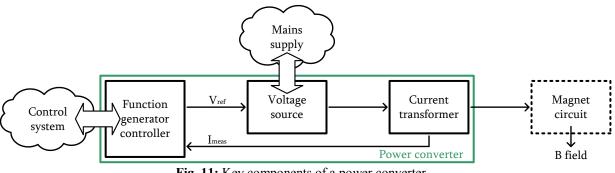

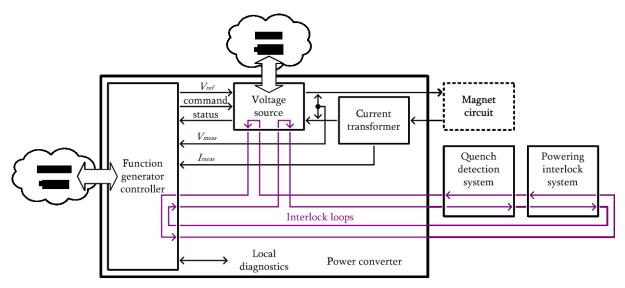

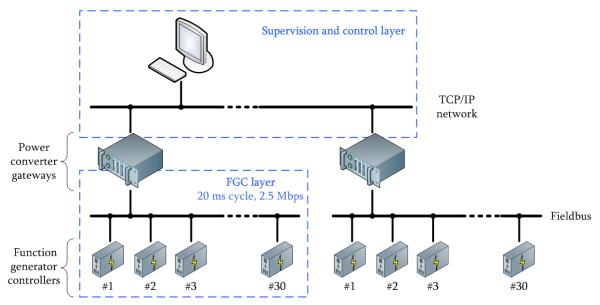

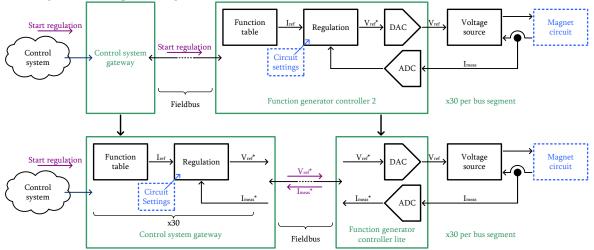

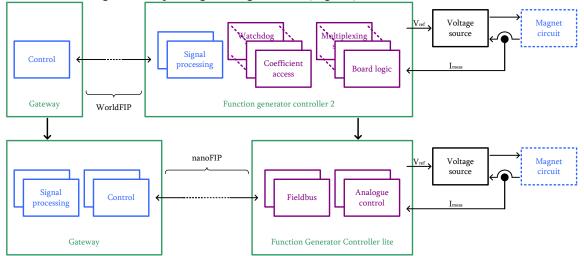

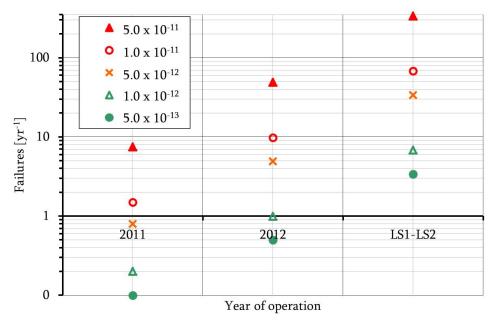

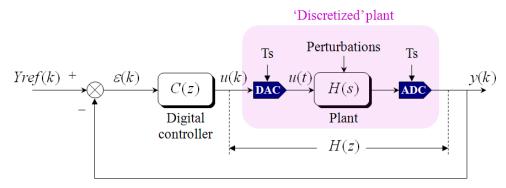

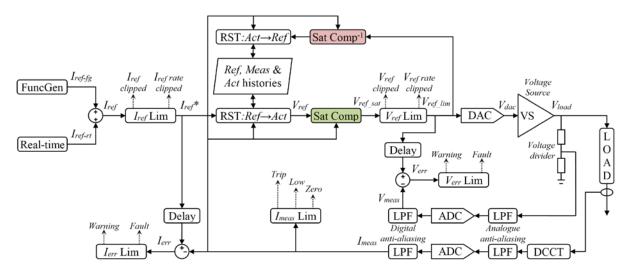

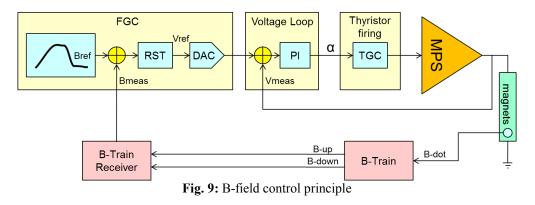

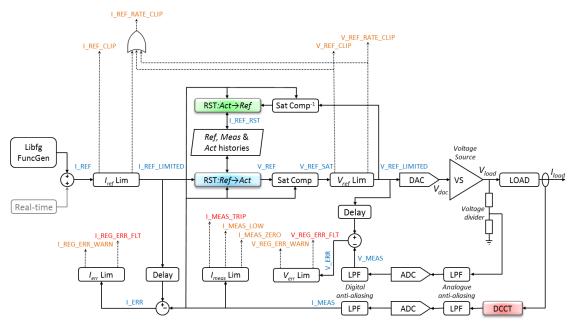

Power converters are always of the current control type, and the control principle is shown in Fig. 18. The power converter receives a current reference from the control room that needs to be executed with precise timing. All of the machine's magnets need to be synchronized, and a central timing system is distributed to all power converters and other accelerator devices. The precise execution of the current reference is one of the most challenging aspects of the control system.

The performance of the current control can be monitored through the tracking error, which is the ability of the power converter to follow the reference function. The static part of the tracking error is linked to static performance (accuracy and reproducibility). The dynamic part comes from timing error and regulation lagging error. All of these requirements lead to a definition for the power converter controller.

Fig. 18: Principle of power converter control

## 4.2 High precision

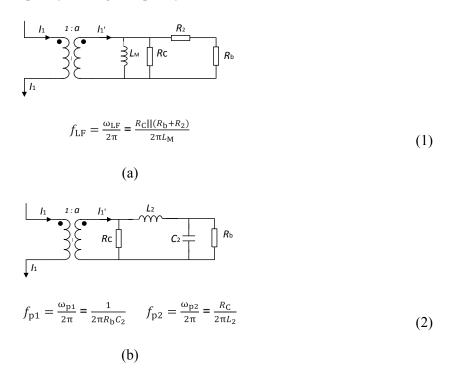

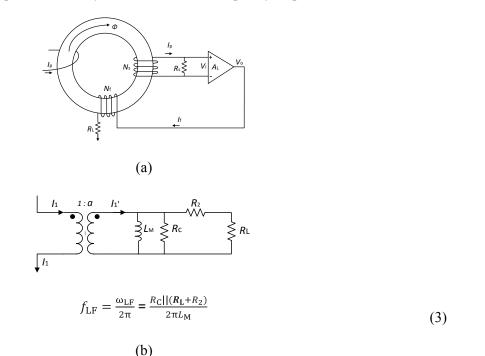

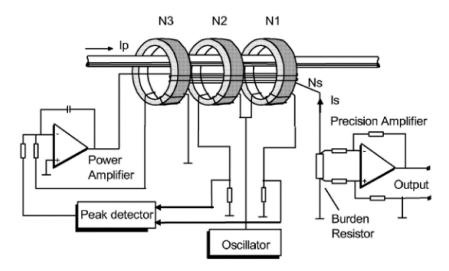

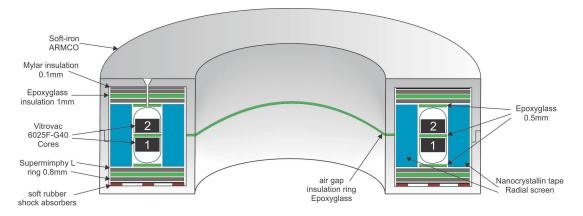

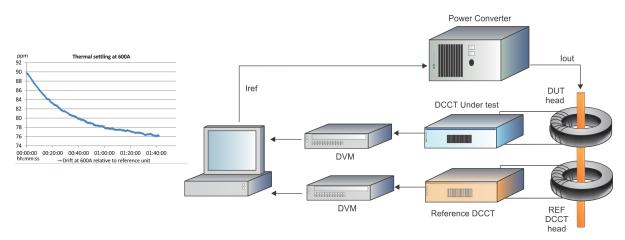

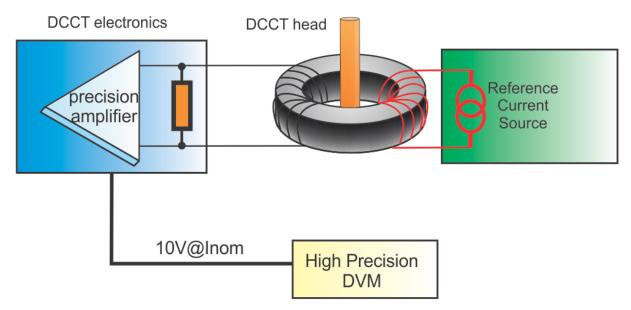

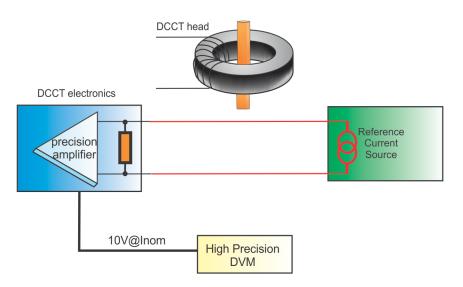

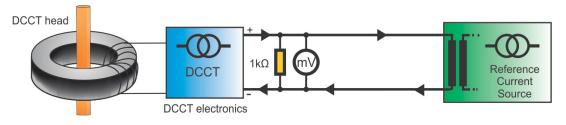

To get a high-precision power converter, a device capable of precisely measuring the output current is needed. The most popular current transducer is the DCCT (Direct-Current Current Transducer) for its high performance in many different fields, see Fig. 19. It is also classical to install two devices to be able to monitor any deviations of the currents between them [5].

|                  | DCCTs                                                                                                                                                                                      | Hall effect                                                                                                   | CTs                                                                                               | Rogowsky                                                           | Shunts                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|

|                  |                                                                                                                                                                                            |                                                                                                               | <b>Ø</b>                                                                                          |                                                                    |                                                                  |

| Principle        | Zero flux detection                                                                                                                                                                        | Hall effect                                                                                                   | Faraday's law                                                                                     | Faraday's law                                                      | Ohm's law                                                        |

| Output           | Voltage or current                                                                                                                                                                         | Voltage or current                                                                                            | Voltage                                                                                           | Voltage                                                            | Voltage                                                          |

| Accuracy         | Best devices can reach a few ppm stability and repeatability                                                                                                                               | Best devices can<br>reach 0.1%                                                                                | Typically not better<br>than 1%                                                                   | Typically %, better<br>possible with digital<br>integrators        | Can reach a few ppm for<br>low currents, <% for high<br>currents |

| Ranges           | 50A to 20kA                                                                                                                                                                                | hundreds mA to tens<br>of kA                                                                                  | 50A to 20kA                                                                                       | high currents possible,<br>up to 100kA                             | From <ma to="" to<br="" up="">several kA</ma>                    |

| Bandwidth        | DCkHz for the higher<br>currents, DC100kHz for<br>lower currents                                                                                                                           | DC up to couple<br>hundred kHz                                                                                | Typically 50Hz up to<br>a few hudreds of kHz                                                      | Few Hz possible, up to<br>the MHz                                  | Up to some hundreds of<br>kHz with coaxial<br>assemblies         |

| Isolation        | Yes                                                                                                                                                                                        | Yes                                                                                                           | Yes                                                                                               | Yes                                                                | No                                                               |

| Error<br>sources | Magnetic<br>(remanence, external<br>fields, centering)<br>Burden resistor<br>(thermal settling, stability,<br>linearity, tempco)<br>Output amplifier<br>(stability, noise, CMR,<br>tempco) | Magnetic<br>Burden resistor<br>Output amplifier<br>Hall sensor stability<br>(tempco,<br>piezoelectric effect) | Magnetic<br>(remanence, external<br>fields, centering,<br>magnetizing current)<br>Burden resistor | Magnetic<br>Integrator<br>(offset stability, linearity,<br>tempco) | Power coefficient,<br>tempco, ageing, thermal<br>voltages        |

Fig. 19: Different types of current transducers

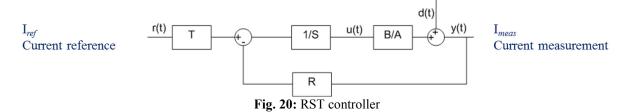

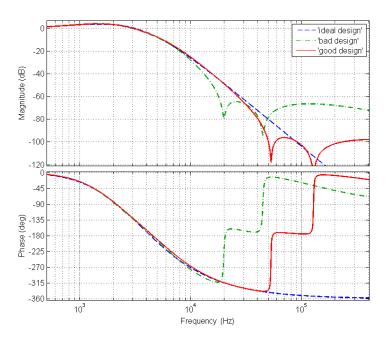

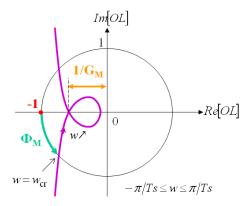

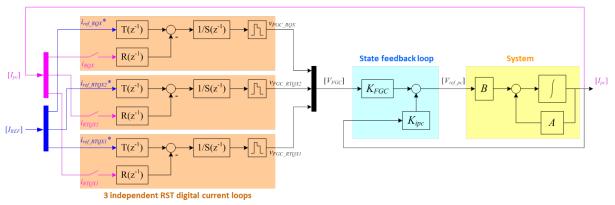

The performance of the power converter also strongly depends upon the current regulation control algorithm. The most powerful algorithm is the RST controller, which allows management of the tracking error as well as regulation, see Fig. 20 [6].

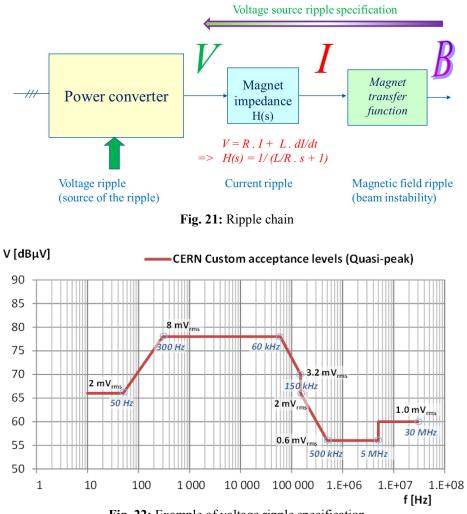

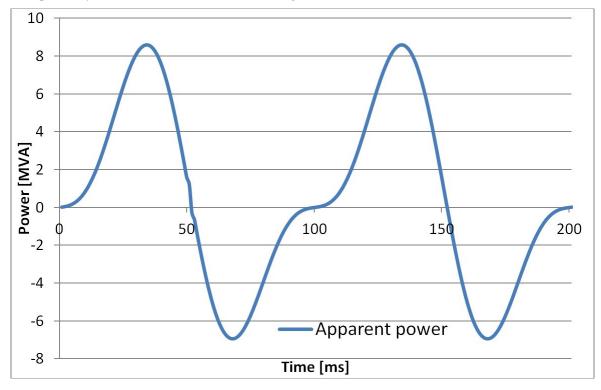

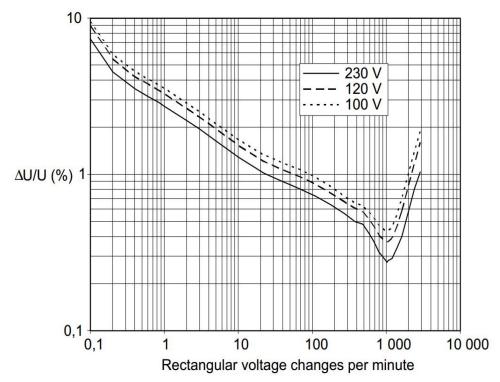

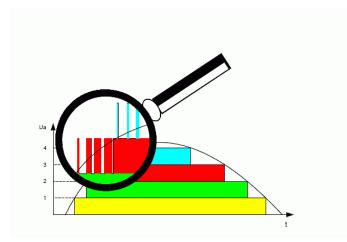

#### 4.3 **Power converter ripple**

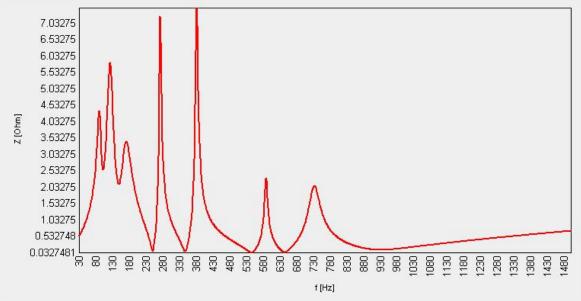

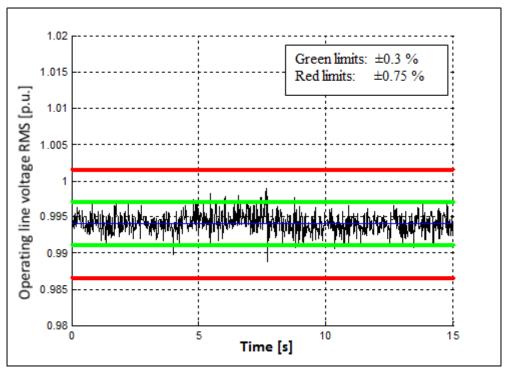

In principle, the voltage delivered by a power converter has a ripple that is due to semiconductor switching. The voltage ripple is generated by the power converter, and it is converted into a magnetic field ripple through the impedance of the magnet. The maximum magnetic field ripple has to be determined by the beam quality requirements, and then from the impedance of the magnet the maximum voltage ripple can be specified, see Fig. 21. The impedance of the vacuum chamber, between the current ripple and the magnetic field ripple, can also be taken into account. Typically, the vacuum chamber has a filtering effect above 100 Hz. The voltage ripple has to be specified for all frequencies, see Fig. 22.

Fig. 22: Example of voltage ripple specification

## 4.4 Functional specification

Before starting the design of a new power converter, a functional specification needs to be approved between the accelerator physicists and the magnet designers. This functional specification includes:

- a short description of the machine;

- a description of the loads: magnet layout, magnet parameters, optimization with integral cost, and energy saving;

- a description of the operation duty cycle: machine cycles, minimum and maximum beam energy, ramp rates, hysteresis management, etc.;

- power converter requirements: power converter rating, current precision, current tracking, control system, energy management, lock-out and safety procedure, infrastructure (layout, electricity, cooling, handling, etc.);

- purchasing and development strategy;

- planning;

- budget;

- resources.

## 5 Introduction to the main challenges

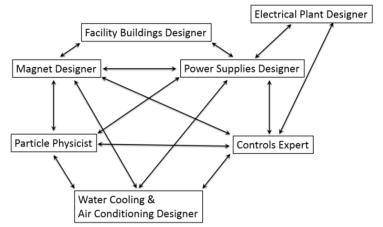

The design of power converters covers a large range of disciplines. It needs more than one specialist to build it, it is a team work. The main challenges are listed below:

- power:

- o power converter topologies;

- o semiconductors, switching frequency, thermal design, fatigue while cycling...

- filtering and electromagnetic compatibility (EMC);

- connection to AC grid and robustness to grid perturbations;

- energy management and energy saving;

- protection and safety of the system;

- control:

- accuracy class;

- digitalization;

- control loops;

- timing and synchronization;

- control interfaces;

- o interlocks with external systems.

## References

D. Einfeld, The new upgrade of SESAME, Proc. EPAC2002, Paris, France, 3-7 June 2002, p. 680, http://accelconf.web.cern.ch/AccelConf/e02/PAPERS/TUPLE027.pdf.

- [2] LHC design report, Vol. 1, edited by O. Bruning et al., CERN-2004-03 (CERN, Geneva, 2004), DOI: http://dx.doi.org/10.5170/CERN-2004-003.

- [3] F. Bordry, LHC inner triplet powering strategy, Proc. PAC01, Chicago, United States, 18-22 June 2001, p. 633, http://accelconf.web.cern.ch/AccelConf/p01/PAPERS/ROPB012.pdf.

- [4] N. Marks, in Proceedings of the CAS-CERN Accelerator School: Specialised Course on power Converters, Warrington, United Kingdom, 12-18 May 2004, edited by D. Brandt, CERN-2006-010 (CERN, Geneva, 2006), pp. 1-12. DOI: http://dx.doi.org/10.5170/CERN-2006-010.

- [5] G. Fernqvist, IEEE Trans. Instrum. Meas. 48(2) (1999) 462.

- [6] F. Bordry, RST digital algorithm for controlling the LHC magnet current, Proc. EP2 Forum '98, Grenoble, France, 21-22 October 1998.

#### **Bibliography**

Proceedings of the CAS-CERN Accelerator School: Power Converters for Particle Accelerators, Montreux, Switzerland, 26-30 March 1990, edited by S. Turner, CERN-1990-007 (CERN, Geneva, 1990), DOI: http://dx.doi.org/10.5170/CERN-1990-007.

Proceedings of the CAS-CERN Accelerator School: Specialised Course on Power Converters, Warrington, United Kingdom, 12-18 May 2004, edited by D. Brandt, CERN-2006-010 (CERN, Geneva, 2004), DOI: http://dx.doi.org/10.5170/CERN-2006-010.

## **Definition of Power Converters**

*F. Bordry and D. Aguglia* CERN, Geneva, Switzerland

## Abstract

The paper is intended to introduce power conversion principles and to define common terms in the domain. The concepts of sources and switches are defined and classified. From the basic laws of source interconnections, a generic method of power converter synthesis is presented. Some examples illustrate this systematic method. Finally, the commutation cell and soft commutation are introduced and discussed.

## Keywords

Power converter; power electronics; semiconductor switches; electrical sources; design rules; topologies.

## 1 Introduction

The task of a power converter is to process and control the flow of electrical energy by supplying voltages and currents in a form that is optimally suited for user loads.

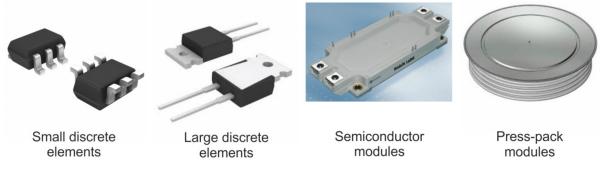

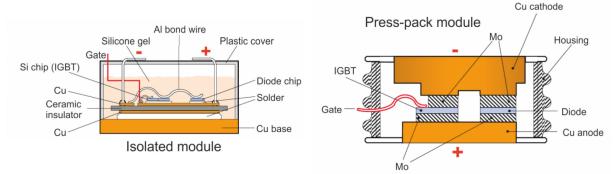

Energy conversions were initially achieved using electromechanical converters (which were mainly rotating machines). Today, with the development and the massive production of power semiconductors, static power converters are used in numerous application domains and especially in particle accelerators. Their weight and volume are smaller and their static and dynamic performance are better.

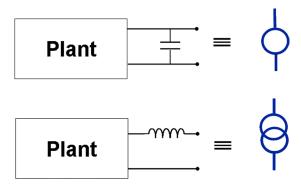

A static converter is composed of a set of electrical components building a meshed network that acts as a linking, adapting, or transforming stage between two sources, generally between a generator and a load (Fig. 1).

Fig. 1: Definition of a power converter

An ideal static converter allows control of the power flow between the two sources with 100% efficiency. A large part of power converter design is the optimization of its efficiency. But as a first approach and to define basic topologies, it is interesting to take the hypothesis that no losses occur

through a power converter's conversion process. With this hypothesis, the basic elements are of two types:

- non-linear elements that are, most of the time, electronic switches: semiconductors used in commutation mode [1];

- linear reactive elements: capacitors, inductances (and mutual inductances or transformers). These reactive components are used for intermediate energy storage but also perform voltage and current filtering. They generally represent an important part of the size, weight and cost of the equipment [2, 3].

The objective of this introductory paper is to recall and give a precise definition of basic concepts essential for the design or understanding of power converter topologies [4]. First, a very simple example is presented to illustrate the basic principle of modern power electronics converters (switching power converter). Then the sources and the switches are defined, followed by the fundamental connection rules between these basic elements. From there, converter topologies are deduced. Some examples of topology synthesis are then given. Finally, the concept of hard and soft commutation is introduced.

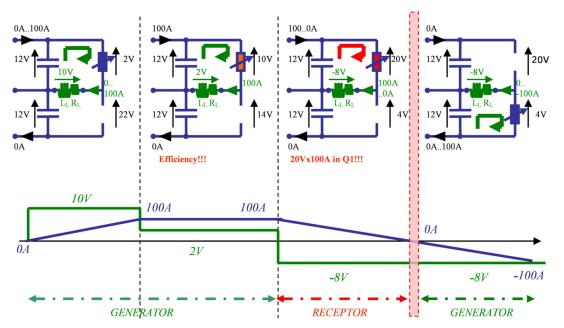

#### 2 The very basic principles of modern power electronics conversion

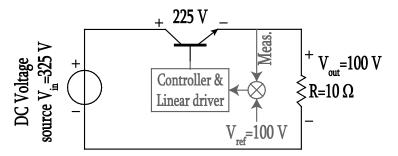

As a first basic example to illustrate the evolution toward modern power electronics, let us consider a DC to DC converter that aims to deliver 100 V to a resistive load of 10  $\Omega$ . The input voltage source delivers a constant 325 V. Until the 1960s, and still in use in some special applications, a typical utilization of transistors consisted of operating them in their linear, or active, region. The basic 'old' topology for this case is illustrated in Fig. 2. This consists of operating the transistor such that a 225 V voltage drop across it is ensured. Simplifying, one can say that in this case the transistor is used as a controllable resistance.

Fig. 2: DC to DC converter using the transistor's linear, or active, region

Analysing this circuit at this operating point, one can derive the input and the delivered output powers  $P_{\text{in}}$  and  $P_{\text{out}}$ , the losses in the transistor  $P_{\text{T}}$ , and the converter efficiency  $\eta$ , as presented in Eq. (1),

$$P_{\rm in} = 325 \,\rm V \,\times\, 10 \,\rm A = 3.25 \,\rm kW \,, \tag{1}$$

$$P_{\rm out} = 100 \,\mathrm{V} \times 10 \,\mathrm{A} = 1 \,\mathrm{kW} \,,$$

(2)

$$P_{\rm T} = P_{\rm in} - P_{\rm out} = 2.25 \,\rm kW$$

, (3)

$$\eta = \frac{P_{\text{out}}}{P_{\text{in}}} = 0.3 \equiv 30\%$$

(4)

Notice that for this particular operating point the efficiency is extremely low. In the general case, the efficiency can be expressed as in Eq. (5), where the efficiency drastically decreases as  $V_{\text{out}}$  decreases,

$$\eta = \frac{P_{\text{out}}}{P_{\text{in}}} = \frac{\frac{V_{\text{out}}^2}{\langle V_{\text{in}} \cdot V_{\text{out}} \rangle_R}}{\frac{V_{\text{out}}}{V_{\text{in}}}} = \frac{V_{\text{out}}}{V_{\text{in}}}.$$

(5)

This conversion system produces high losses and needs an over-dimensioned transistor able to dissipate the losses. Furthermore, the overall dimensions of this power converter shall be large enough

#### DEFINITION OF POWER CONVERTERS

for being able of evacuating the high losses for a given maximum temperature. This conversion method is still used in some special applications where high precision or high dynamics is required [5].

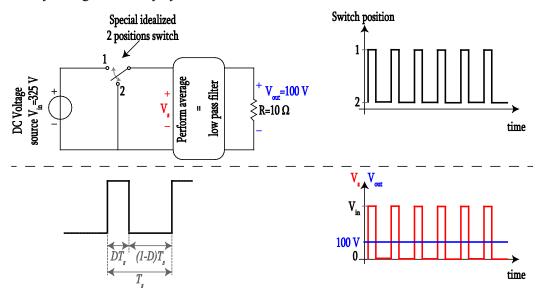

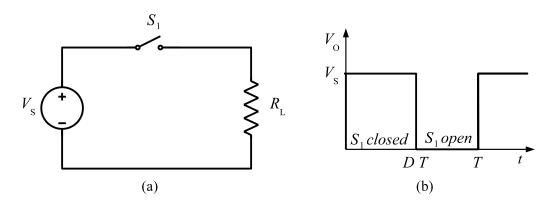

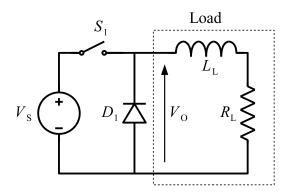

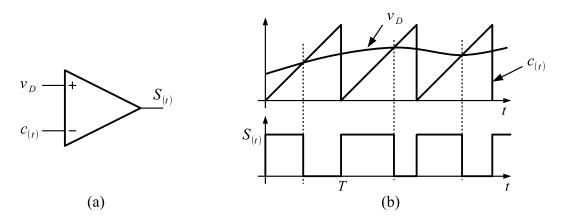

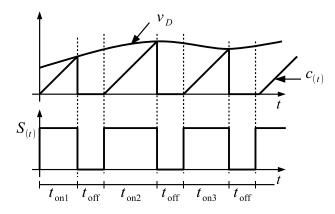

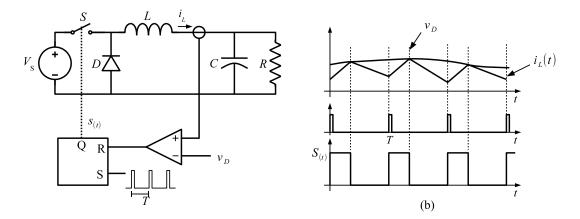

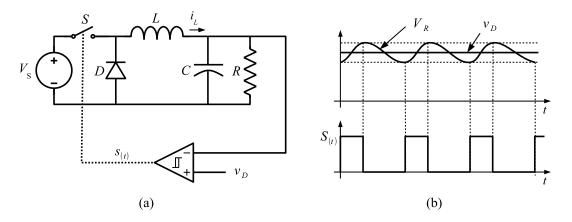

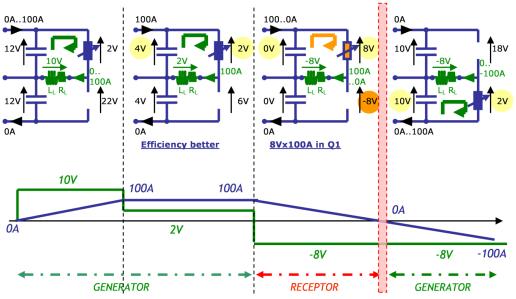

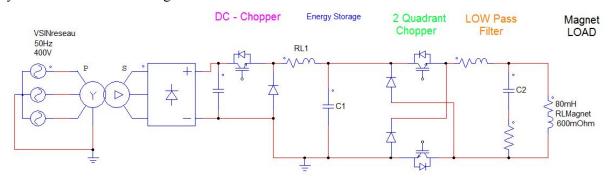

The basic principle of modern power electronics lies in the utilization of switches in their ON and OFF states only, virtually producing no, or very low, losses (losses in switches are described in Section 4.2, Dynamic characteristics). The basic principle is illustrated in Fig. 3. Between the voltage source  $V_{in}$  and the load R, the converter is now composed of a 'special' two-position switch and a low-pass filter. When the switch is in position 1, the input voltage  $V_{in}$  appears at the low-pass filter input  $V_s$ . When the switch is in position 2, zero volts are applied to  $V_s$ . Given a pattern in time of the switch positions, one derives the pattern of the voltage  $V_s$  (chopped or switched voltage). In most applications, the voltage  $V_s$ , with a fluctuation of 100% (from 0 V to  $V_{in}$ ), cannot be directly applied to the load, therefore a filtering action must be undertaken in order to apply the voltage  $V_s$  average values to the load, which is derived in Eq. (6),

$$V_{\rm out} = \frac{1}{T_{\rm s}} \int_0^{T_{\rm s}} v_{in}(t) dt = DV_{\rm in} , \qquad (6)$$

where  $T_s$  is the switching period (which defines the switching frequency  $f_s$ ), and D is the duty cycle, or duty ratio, which defines the relative time when the switch is in position 1 with respect to the switching period  $T_s$  (illustrative definitions are given in Fig. 3). In this case, the regulation of the output voltage is performed by acting on the duty cycle D.

Fig. 3: Idealized switch-mode DC-to-DC converter principle

Thanks to the low losses, modern switch-mode power converters are more efficient and compact. However several new aspects have to be considered during the design phase. A filtering process is required, leading to the introduction of the so-called output voltage and current ripples on the load and voltage, or current, bandwidths. A non-ideal filter is always letting some harmonics pass through the load. Furthermore, the dynamic characteristics of the power converter (rate of change of current and/or voltage) is limited by the filter. This trade-off between ripple and bandwidth is a key aspect in the design and specification process of modern switch-mode power converters.

#### 3 Sources

As mentioned in the introduction, a power converter processes the flow of energy between two sources. To synthesise a power converter topology, the first step is to characterize these sources. We will see later that the converter structure can be directly deduced as soon as the sources are defined: voltage or current sources and their reversibilities.

In the energy conversion process, a source is usually a generator (often called an input source) or a load (often called an output source). However, in the case of a change of direction of the energy flow, i.e. a change in the sign of the power, the sources (generators and loads) can exchange their functions (i.e. restoration of energy from a magnet back to the grid).

#### 3.1 Nature of sources

#### 3.1.1 Definitions

Two types of sources could be defined: voltage and current sources. As mentioned, any of these sources could be a generator or a receiver (load).

A source is called a *voltage* source if it is able to impose a voltage independently of the current flowing through it. This implies that the series impedance of the source is zero (or negligible in comparison with the load impedance)

A source is called a *current* source if it is able to impose a current independently of the voltage at its terminals. This implies that the series impedance of the source is infinite (or very large in comparison with the load impedance).

These definitions correspond to permanent properties. The principle of operation of a converter is based on the switch-mode action of its switches. Commutation of the switches generates very fast current and/or voltage transients so that the transient behaviour of the sources is of fundamental importance for the converter design. The transient behaviour of a source is characterized by its ability or inability to withstand steps in the voltage across its terminal or in the current flowing through it, these steps being generated by the external circuit. Then new definitions could be stated as below.

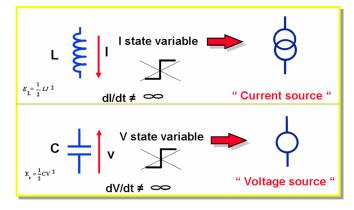

- A source is a *voltage source* if the voltage across its terminals cannot undergo a discontinuity due to the external circuit variation. The most representative example is a capacitor, since an instantaneous change of voltage would correspond to an instantaneous change of its charge that would require an infinite current (Fig. 4(b)).

- A source is a *current source* if the current flowing through it cannot undergo a discontinuity due to the external circuit variation. The most representative example is an inductor, since an instantaneous change in current would correspond to an instantaneous change in its flux that would require an infinite voltage (Fig. 4(a)).

Fig. 4: Inductance and capacitor vs. current and voltage source

It should be noted that a square wave voltage generator is indeed a voltage source as defined above since the voltage steps are not caused by the external circuit. A square wave current generator is indeed a current source as defined above since the current steps are not caused by the external circuit.

With these definitions, it is interesting to define the notion of instantaneous impedance of a source as the limit of the source impedance when the Laplace operator tends towards infinity. Theoretically this instantaneous impedance can be zero, finite, or infinite.

A source is referred to as a voltage source when its instantaneous impedance is zero, while a source is called a current source if its instantaneous impedance is infinite.

#### For example:

| Capacitor:    | Z(s) = 1/(C.s) | , limit $s \to \infty$ | Z(s) = 0, this leads to a voltage source;         |

|---------------|----------------|------------------------|---------------------------------------------------|

| Inductance:   | Z(s) = L.s ,   | $\lim_{s \to 0} t$     | $Z(s) = \infty$ , this leads to a current source. |

| 1 2 Source re |                | 5 / 0                  |                                                   |

#### 3.1.2 Source reversibility

The determination of the source reversibilities is fundamental. We will see that the reversibility analysis allows the deduction of the static characteristics of the switches.

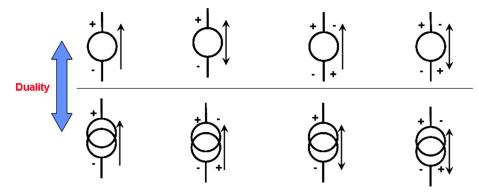

The voltage (or the current) that characterizes a source is termed DC if it is unidirectional. As a first approximation, it can be taken as being constant. The voltage (or the current) is termed AC if it is periodic and has an average value equal to zero. As a first approximation, it can be taken as sinusoidal.

A source is voltage-reversible if the voltage across its terminals can change sign. In the same way, a source is current-reversible if the current flowing through it can reverse.

In summary, the input/output of a converter can be characterized as voltage or current sources (generator or loads), either DC or AC, current-reversible and/or voltage-reversible. In total, there are only eight possibilities, shown in Fig. 5.

Fig. 5: Voltage and current sources with their reversibilities

#### 3.1.3 Source nature modification

Connection of a series inductance with an appropriate value to a voltage source (i.e. a dipole with zero instantaneous impedance) turns the voltage source into a current source. In the same way, connecting a parallel capacitor of appropriate value to a current source (a dipole with infinite instantaneous impedance) turns the current source into a voltage source (Fig. 6).

Fig. 6: Source nature confirmation or modification

These inductive or capacitive elements connected in parallel or in series with the source are elements that can temporarily store energy. Consequently, if an inductance connected to a voltage source turns it into a current source it is important to determine the current reversibility of this current source.

In practice the identification of a real generator or of a real load as a voltage or current source is not obvious. That is the reason why the nature of the source is often reinforced by the addition of a parallel capacitor in the case of voltage sources and by the addition of a series inductor in the case of current sources.

Obviously, the current source obtained by connecting an inductance in series with a voltage source keeps the same current reversibility as this voltage source. The inductance acts as a buffer absorbing the voltage differences. Consequently the current source obtained by connecting a series inductance to a voltage source is reversible in voltage. When the voltage source itself is reversible in voltage there is no particular problem. But, if the voltage source is not reversible in voltage, the current source obtained by connecting a series inductance to the voltage source is only instantaneously reversible with respect to voltage.

The former result can easily be transposed to the voltage source obtained by the parallel connection of a capacitor to a current source. The voltage source obtained keeps the same voltage reversibility as the current source and is reversible in current. However, this reversibility is only instantaneous if the current source is not reversible in current.

#### 3.1.4 Example

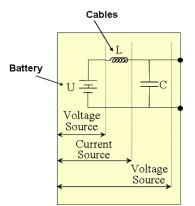

A set of ideal batteries behaves as a load during charging and as a generator during discharging; such a source is called a DC voltage source, being current reversible but not voltage reversible. Nevertheless, because of the inductance of the connecting cables, this battery can sometimes be taken as a current source that is instantaneously voltage reversible and permanently current reversible. If a capacitor bank is added at the terminals of the cables, it again becomes a voltage source (Fig. 7).

Fig. 7: Modification to voltage or current source

#### 4 Switch characteristics

Static converters are electrical networks mainly composed of semiconductor devices operating in switch mode (as switches). Through proper sequential operation of these components, they allow an energy transfer between two sources with different electrical properties.

The losses in the switches should be minimized in order to maximize the efficiency of the converter. Switches must have a voltage drop (or an ON resistance) as low as possible in the ON state, and a negligible leakage current (or an OFF resistance) in the OFF state. These two states are defined as static states.

#### **DEFINITION OF POWER CONVERTERS**

The change from one state to the other state (switch commutation) implies transient behaviour of the switch. These behaviours are complex because they depend on the control of the switch (through a gate control) and on the conditions imposed by the external circuit.

#### 4.1 Static characteristics

In the static domain a switch has the same behaviour as a non-linear resistance: very low in the ON state and very high in the OFF state.

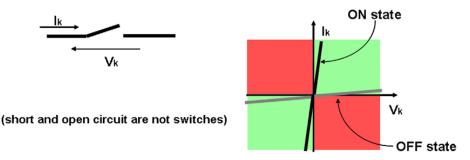

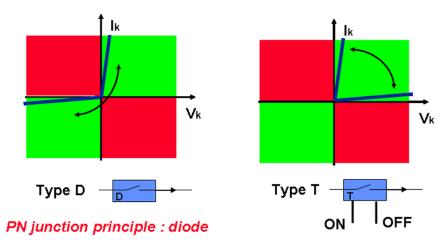

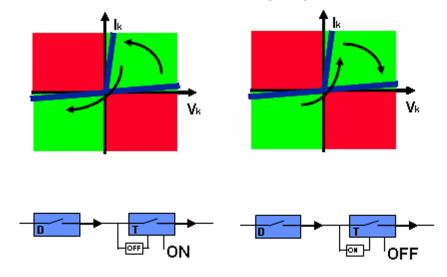

Taken as a dipole with the load sign convention (Fig. 8) the static characteristic  $I_k(V_k)$ , which represents the operating points of a switch, is made up of two branches totally located in quadrants 1 and 3 such that  $(V_k \times I_k) > 0$ . One of these branches is very close to the  $I_k$  axis (ON state) and the other is very close to the  $V_k$  axis (OFF state). Each of these branches can be located in one or two quadrants. In the case of an ideal switch, the static characteristics are the half-axis to which they are close.

Fig. 8: Static characteristics of a switch

In this representation, except for the obvious cases of a short circuit and of an open circuit that correspond respectively to a switch always ON and to a switch always OFF, any switch that really behaves as a switch (commutation: ON <=> OFF) has a static characteristic consisting of at least two orthogonal half-axes (or segments).

The static characteristic, an intrinsic feature of a switch, reduces to a certain number of segments in the  $I_k(V_k)$  plane.

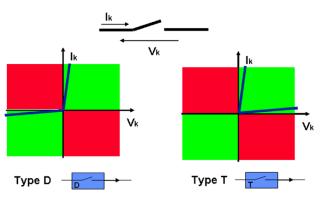

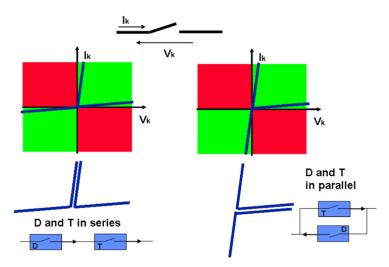

- Two-segment characteristics: the switch is unidirectional in current and in voltage. Two twosegment characteristics can be distinguished: in the first case, current  $I_k$  and voltage  $V_k$  have the same signs; in the second case, current  $I_k$  and voltage  $V_k$  have opposite signs. The switches having such characteristics are respectively called T and D switches (Fig. 9).

Fig. 9: Static characteristics of a two-segment switch

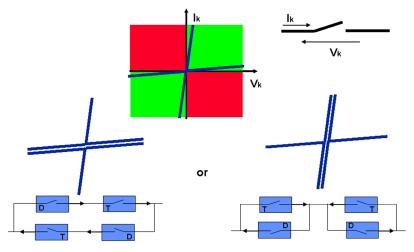

Three-segment characteristics: the switch is bidirectional either in current or in voltage while the other is unidirectional. Therefore, there are two types of three-segment static characteristics (Fig. 10). It should be noted that these two types of switches could be synthesized with the association in parallel or in series of two-segment switches (T and D).

Fig. 10: Static characteristics of a three-segment switch

Four-segment characteristics: the switch is bidirectional in voltage and in current. There is only

one such type of static characteristic (Fig. 11). A four-segment characteristic could be obtained

by series or parallel connection of switches with three-segment characteristics.

Fig. 11: Static characteristics of a four-segment switch

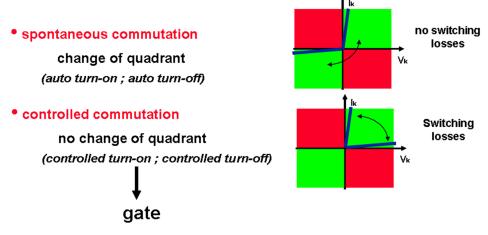

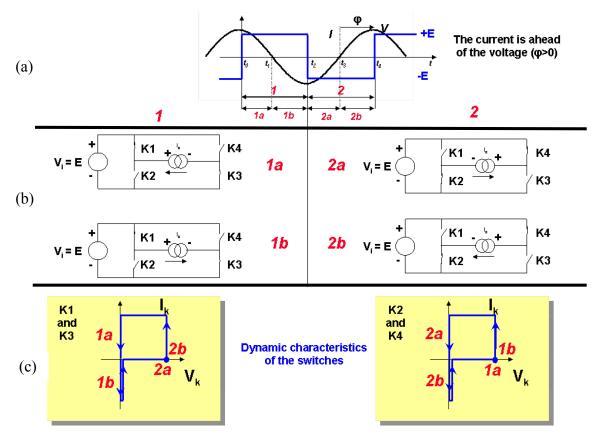

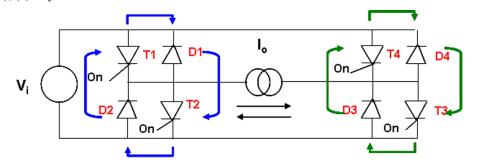

## 4.2 Dynamic characteristics

The dynamic characteristic is the trajectory described by the point of operation of the switch during its commutation, to go from one half-axis to the perpendicular half-axis. A switch being either ON or OFF, there are two commutation dynamic characteristics corresponding to the turn-ON and the turn-OFF, which will be grouped under the global term dynamic characteristics.

Unlike the static characteristic, the dynamic characteristic is not an intrinsic property of the switch but also depends on the constraints imposed by the external circuit. Neglecting second-order phenomena, and taking into account the dissipative nature of the switch, the dynamic characteristic can only be located in those quadrants where  $V_k \times I_k > 0$  (generator quadrants). For the two commutations (turn-ON and turn-OFF), two modes are possible: controlled commutation and spontaneous commutation.

## 4.2.1 Controlled commutation

The switch has, in addition to its two main terminals, a control terminal on which it is possible to act in order to provoke a quasi-instantaneous change of state (in the case of a T switch). The internal resistance

of this switch can change from a very low value to a very high value at turn-OFF (and inversely at turn-ON). These changes are independent of the evolution of the electrical quantities imposed on the switch by the external circuit.

It should be noted that, in a controlled commutation, the switch imposes its state on the external circuit. Under such circumstances, the element can undergo severe stresses that depend on its dynamic characteristic. If the switching time is long and the operating frequency is high, the commutation losses can be important.

## 4.2.2 Spontaneous commutation

The spontaneous commutations correspond to turn-OFF when the current flowing through the switch arrives at zero and to turn-ON when the voltage applied across its terminals reaches zero. Spontaneous commutation is the commutation of a simple PN junction (D switch). It is only dependent on the evolution of the electrical variables in the external circuit. Spontaneous commutations could be achieved with any controlled semiconductor if the gate control is synchronized with the electrical quantities of the external circuit. Spontaneous commutations could be achieved moves along the axes.

It is important to point out that controlled commutation can only happen in the first or third quadrants while spontaneous commutation can only happen with a change of quadrant (Fig. 12).

Fig. 12: Spontaneous and controlled commutations

## 4.3 Classification of switches

Finally, switches used in power converter can be classified by their static characteristics (two, three or four segments) and by the type of commutation (controlled or spontaneous) at turn-ON and at turn-OFF.

## 4.3.1 Two-segment switches

Except the open circuit and the short circuit, two switches with two-segment characteristics can be distinguished (Fig. 13).

- The first of these switches has the static characteristics of switch D, and its turn-ON and turn-OFF commutations are spontaneous. This switch is typically a diode.

- The second of these switches has the static characteristics of switch T and its turn-ON and turn-OFF commutations are controlled. Examples are the power semiconductors: metal-oxide semiconductior field-effect transistors (MOSFET), insulated-gate bipolar transistor (IGBT), gate turn-off thyristor (GTO), integrated-gate commutated thyristor (IGCT), etc.

Fig.13: Dynamic characteristics of two-segment switches

This switch will be symbolized by separating the turn-ON and turn-OFF control gate as shown in Fig. 13.

A switch with two-segment characteristics similar to the T type (both segments in the same quadrant), must have controlled turn-ON and turn-OFF commutations. If it would have only one controlled commutation, it would be necessary to put in series or in parallel a switch D (a diode) to get the spontaneous commutation. In this case, it is no longer a two-segment switch, but a three-segment one. Therefore, only two two-segment switches can be used directly.

4.3.2 Three-segment switches

These switches can be divided into two groups depending whether they are:

- unidirectional in current and bidirectional in voltage (Fig. 14);

- bidirectional in current and unidirectional in voltage (Fig. 15).

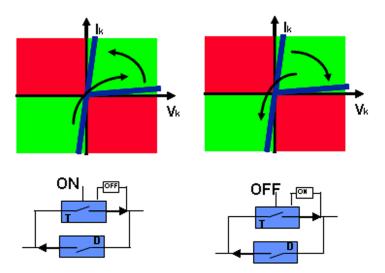

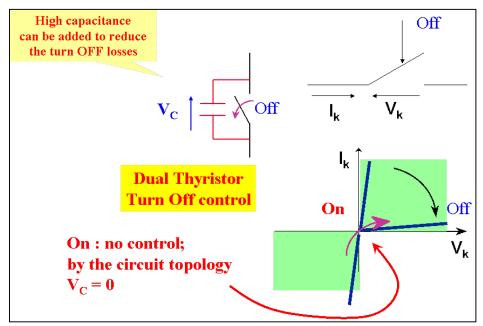

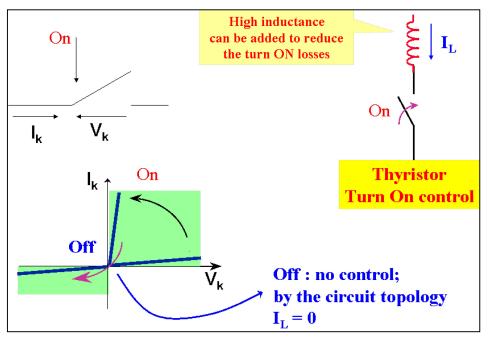

Fig, 14: Dynamic characteristics of three-segment switches: bidirectional in voltage

Fig. 15: Dynamic characteristics of three-segment switches: bidirectional in current

Except for the thyristor, all these switches are synthesized switches, realized by connecting a diode in parallel or in series with a two-segment switch. A special driver is needed to obtain spontaneous commutation. The 'dual-thyristor' (unidirectional in voltage, bidirectional in current, controlled turn-OFF and spontaneous turn-ON) is a good example of a useful three-segment switch [6, 7].

In each of these two groups, all switches have the same static characteristics but differ with their commutation mechanisms. It is important to remark that if a three-segment switch has both commutations controlled (turn-ON and turn-OFF) or both spontaneous, it would never use the three segments of its static characteristic. Therefore, a three-segment switch must necessarily have one controlled commutation and one spontaneous commutation.

The cycle of operation, which represents the locus described by the point of operation of these switches, is then fully determined. They can only be used in converter topologies that impose a single cycle on the switches during operation.

## 4.3.3 Four-segment switches

All four-segment switches have the same static characteristic. They differ only by their commutation modes that can, a priori, differ in quadrants 1 and 3. So, six four-segment switches can be distinguished.

These switches are used mainly in direct frequency changers and in matrix converters; in practice they are made up of two three-segment switches connected in series or parallel.

## 5 Interconnection of sources: Commutation rules

To control the power flow between two sources, the operation principle of a static power converter is based on the control of switches (turn-ON and turn-OFF) with determined cycles creating periodic modifications of the interconnection between these two sources.

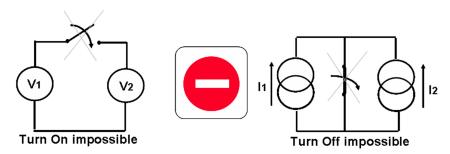

The source interconnection laws can be expressed in a very simple way:

- a voltage source should never be short-circuited but it can be open-circuited;

- a current source should never be open-circuited but it can be short-circuited.

From these two general laws, it can be deduced that switches cannot establish a direct connection between two voltage sources or between two current sources.

Fig. 16: Basic interdictions of source interconnection

In the case of two voltage sources, the switch turn-ON can only happen when the two sources have the same values, that is to say at the zero crossing of the voltage across the switch. The turn-ON must then be spontaneous (since it depends on the external circuit) and turn-OFF can be controlled at any time. In the case of two current sources, the switch turn-OFF can only happen when the two current sources reach the same value, that is to say when the current in the switch reaches zero. In this case, the turn-OFF is spontaneous and turn-ON can be controlled at any time.

As it is done in day-to-day practise and following the previous arguments, it is obvious that it is possible to put capacitors in parallel and inductances in series but these elements should be connected with zero voltage or zero current, respectively.

From the laws state above, it is easy to deduce that the commutation of switches must not interconnect two sources of the same nature.

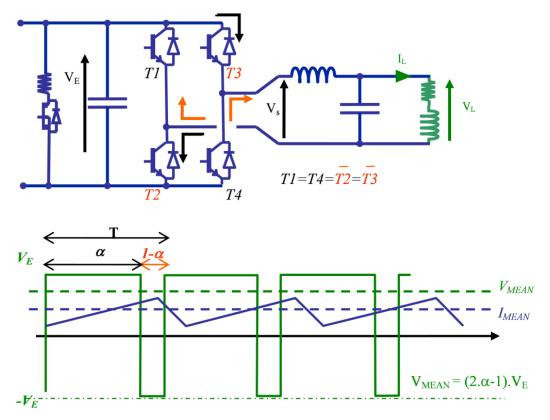

## 6 Structure of power converters

A power converter can be designed with different topologies and with one or several intermediate conversion stages. When this conversion is achieved without any intermediate stage temporarily storing some energy, the conversion is called direct conversion and it is achieved by a direct converter. On the other hand, when this conversion makes use of one or more stages able to store energy temporarily, the conversion is termed indirect and it is achieved by an indirect converter.

The interdiction to connect two sources of the same nature leads to the consideration of two classes of basic conversion topologies:

- direct link topology: when the two sources have different natures;

- indirect link topology: when the two sources have the same nature.

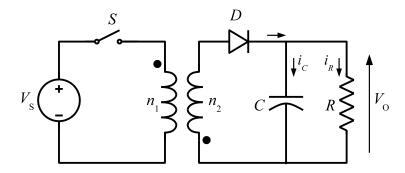

## 6.1 Direct link topology converters

A direct converter is an electrical network composed only of switches and is unable to store energy. In such a converter, the energy is directly transferred from the input to the output (with the hypothesis that the losses can be neglected); the input power is at any time equal to the output power.

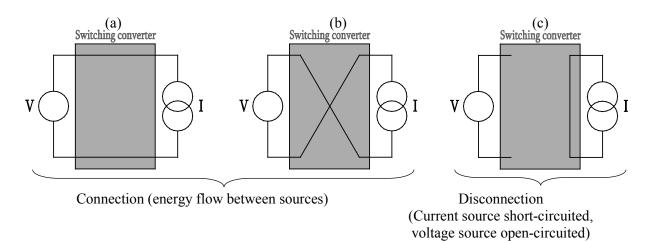

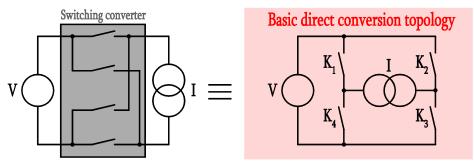

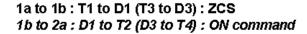

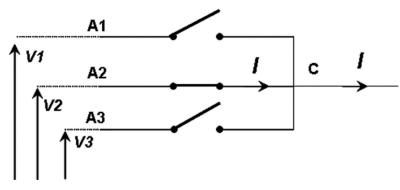

Taking into account the interconnection rules recalled above, the different possible connections between a voltage source and a current source are shown in Fig. 17. To get all these connections, the simplest structure is the four-switches bridge (Fig. 18):

- with K1 and K3 closed, the connection shown in Fig. 17(a) is obtained;

- with K2 and K4 closed, the connection shown in Fig. 17(b) is obtained;

- with K1 and K2 closed (or with K3 and K4 closed), the connection shown in Fig. 17(c) is obtained.

**Fig. 17:** Interconnection possibilities between a voltage and a current source. (a) – direct connection; (b) – inverse connection; (c) - disconnection with current source in short-circuit.

Fig. 18: Basic configuration of voltage-current direct converter

When some of these connections are not necessary, it is possible to simplify the bridge structure into structures using fewer switches (i.e. a buck converter).

Energy conversion between an input current source and an output voltage source is the same problem. The basic configuration is the same but it is more usual to represent the input source on the left and the output source on the right (Fig. 19).

Fig. 19: Basic configuration of current–voltage direct converter

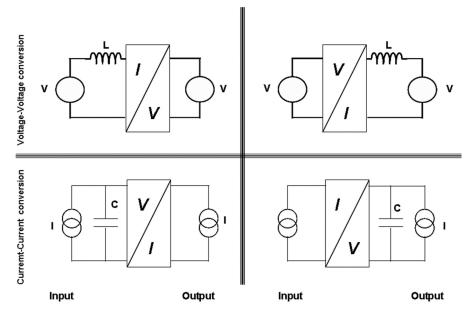

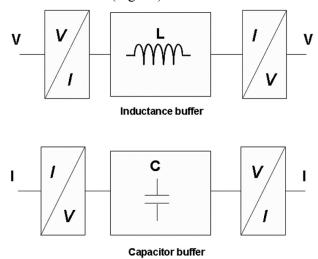

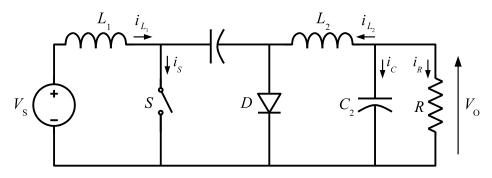

## 6.2 Indirect converters

If both sources have the same nature, it is not possible to interconnect them directly with switches. It is necessary to add components to generate an intermediate buffer stage of a different type without active energy consumption (capacitor or inductor). This buffer stage is a voltage source (capacitor) if the energy transfer is between two current sources, and it is a current source (inductance) if the energy transfer is between two voltage sources.

#### 6.2.1 Modification of the nature of the input or output source

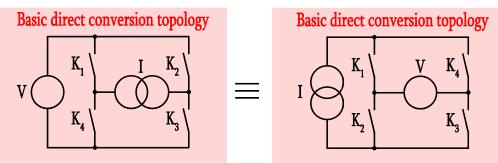

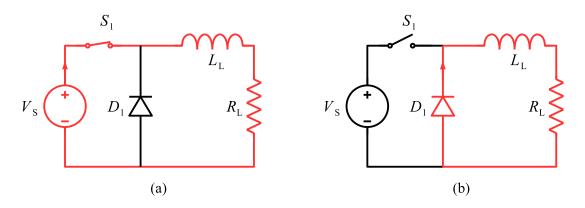

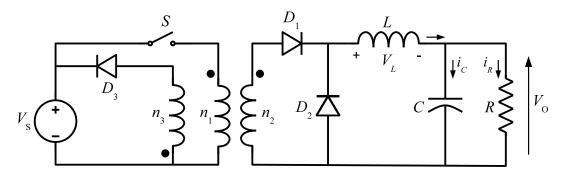

In the case of voltage–voltage conversion, one solution could be to add an inductance in series with the input voltage source or with the output voltage source. With this change of the source nature, it is possible to use a direct converter: a current–voltage or voltage–current converter according to where the inductance was added (Fig. 20).

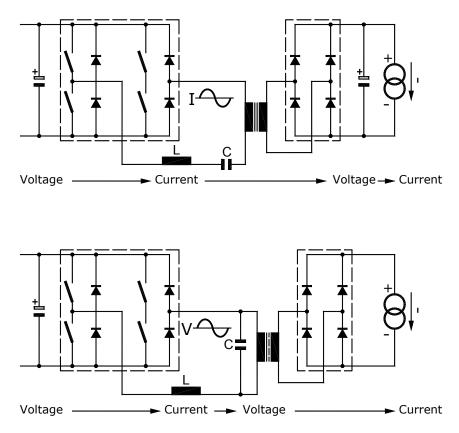

**Fig. 20:** Indirect converters: modification of the nature of the input or output source. Above one of the voltage sources need to be modified into a current source. Below one of the current sources need to be modified into a voltage source.

The case of current–current conversion is similar to the previous case. Therefore, a capacitor should be added in parallel or in series with the input current source or with the output current source.

#### 6.2.2 Use of two direct converters

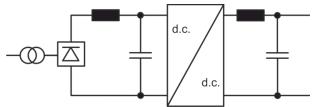

If it is not possible or too costly to modify the nature of one source, two direct converters can be connected with an intermediate buffer stage: an inductance for a voltage–voltage conversion and a capacitor for a current–current conversion (Fig. 21).

Fig. 21: Indirect converters: intermediate buffer stage, inductive above and capacitive below, between two direct converters.

## 6.2.3 Voltage–voltage indirect converters

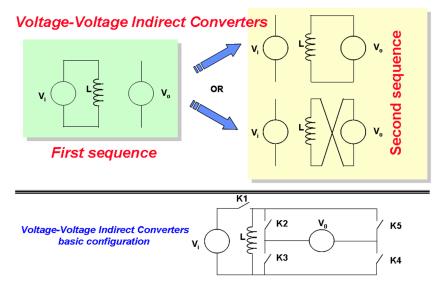

In indirect converters, the two voltage sources are never connected directly (see the basic laws described above). Two sequences are therefore necessary. During the first sequence, the energy is transferred from the input voltage source to the inductance (voltage to current conversion). During the second sequence, the inductance gives back the energy to the output voltage source (current to voltage conversion; two directions are possible) (Fig. 22). An extra switch is necessary to obtain these sequences.

Fig. 22: Voltage–voltage indirect converters. Above the three possible connections between first and second sequences. Below the corresponding topology.

## 6.2.4 Current–current indirect converters

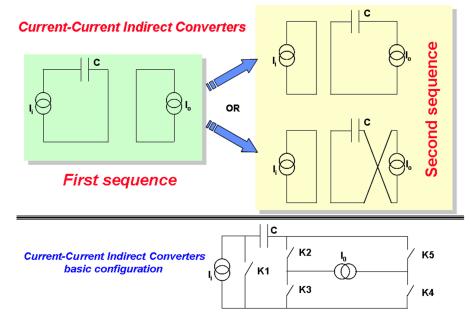

In the indirect converters, the two current sources are never connected directly. Then, two sequences are necessary. During the first sequence, the energy is transferred from the input current source to the capacitor (current to voltage conversion). During the second sequence, the capacitor gives back the energy to the output current source (voltage to current conversion; two directions are possible) (Fig. 23).

Fig. 23: Current–current indirect converters. Above the three possible connections between first and second sequences. Below the corresponding topology.

### 6.3 Conclusions

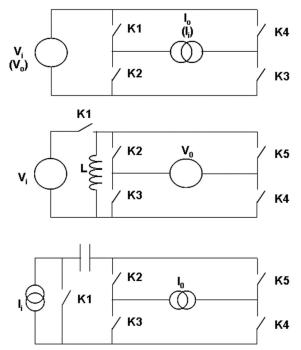

Figure 24 represents the three basic configurations of all single-phase converters.

Fig. 24: Three basic structures of single-phase power converters. Voltage to current (and vice-versa) direct conversion (above), voltage to voltage indirect conversion (in the middle), and current to current indirect conversion (below).

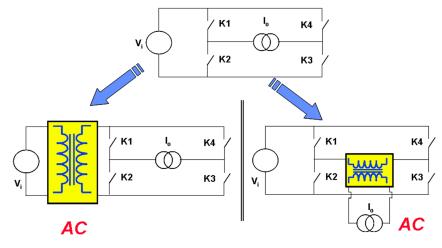

From these basic configurations, it is possible, according to the nature of the sources, to associate them or to add other components. For example, in the case where one of the sources is AC, it is possible to insert a transformer for adaptation or galvanic insulation (Fig. 25).

Fig. 25: Insertion of a transformer in a direct topology

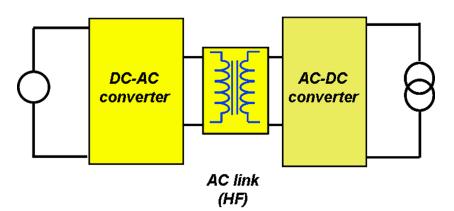

It is also possible to associate several basic topologies. One application that is more frequently used is to have an intermediate stage operating at a high frequency to reduce the size of the transformers and magnetic elements and to get higher performance at the output (bandwidth, ripple, etc.) (Fig. 26). Details of magnetic component design are given in Ref. [3].

Fig. 26: Association of elementary structures

Figure 27 illustrates the case of resonant converters [8, 9]. It should be noted that the interconnection of the various intermediate sources must respect the interconnection laws. It is especially important for the choice of the output filter.

Fig. 27: Series (above) and parallel (below) resonant converters

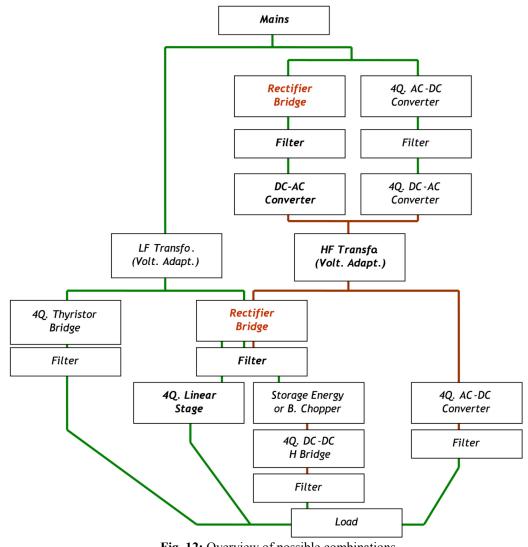

## 7 Power converter classification

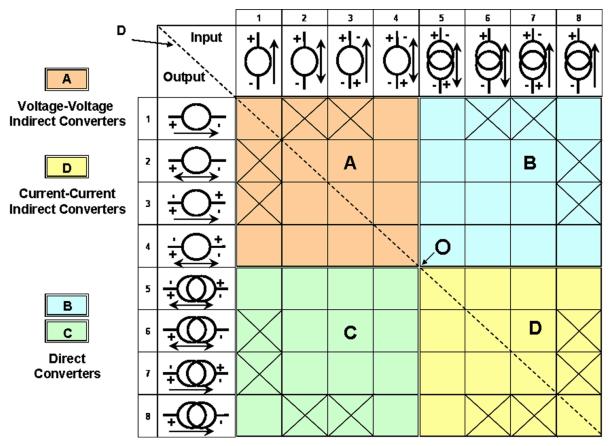

Figure 28 is a table summarizing the power conversion topologies. The crossed cells correspond to reversibility incompatibilities between the input and output sources. Two symmetric cells, with respect to the diagonal line D, represent two reversible topologies. Two topologies corresponding to two cells symmetric with respect to the point O are dual.

Fig. 28: General power conversion table

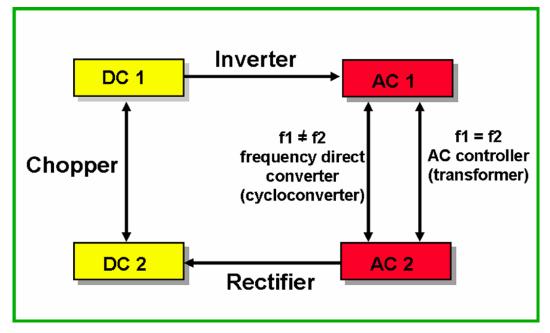

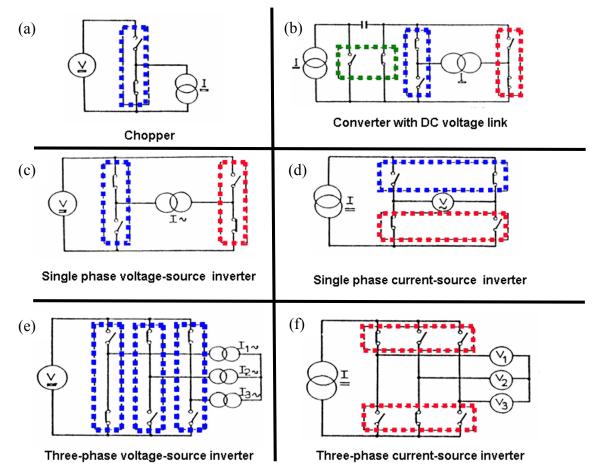

Figure 29 gives the different types of power converters and their usual names.

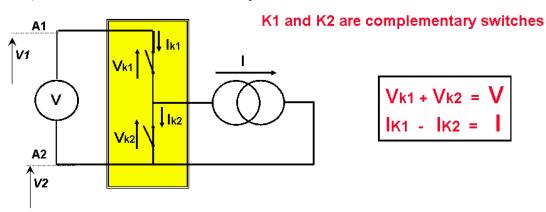

Fig. 29: Power converter classification

## 8 Synthesis of power converters

## 8.1 Synthesis method

A general and systematic method to obtain the power converter topologies is given below.

- 1. Determine the natures of the input and output sources. The basic structure can then be chosen (Fig. 24).

- 2. From the specification, deduce the voltage and current reversibilities of the input and output sources (one configuration from the general table (Fig. 28)).

- 3. From the basic structure, identify the different phases of operation according to the reversibilities and the energy transfer control. If necessary, simplify the configuration (short-circuit or open switches).

- 4. For the various phases, check the sign of the current through the ON switches and the sign of the voltage across the OFF switches: the static characteristics  $I_k(V_k)$  of each switches are defined.

- 5. From the specification (desired output current and/or voltage functions), deduce the sequence of the different phases. For every commutation, represent the working point of each switch before and after the commutation.

- 6. From the static and dynamic characteristics, choose the type of switches (semiconductor type).

## 8.2 Examples

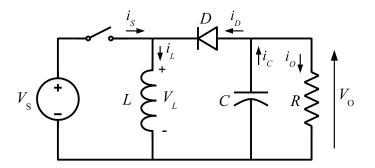

8.2.1 Non-reversible current chopper

Hypothesis:

- power conversion between a voltage source and a current source;

- these two sources are unidirectional in voltage and in current.

Following the steps of the synthesis method:

- 1. a direct converter topology can be used;

- 2. cell (1,8) of the general table according to the source reversibilities;

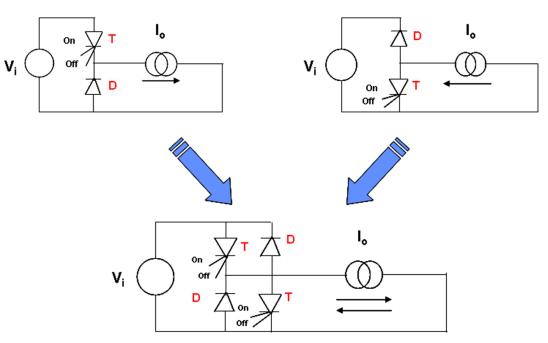

- 3. Sequence 1 (active phase) and 2 (free wheel phase) from Fig. 30;

- 4. the different plots for the four switches for the two sequences are represented in Fig. 30;

- 5. from the previous plots, it can be easily deduced that:

- K1 is a controlled two-segment switch (T switch) (Fig. 13);

- K2 is an inverse D switch;

- K3 is a short-circuit;

- K4 is an open-circuit.

The topology of the converter is thus fully determined.

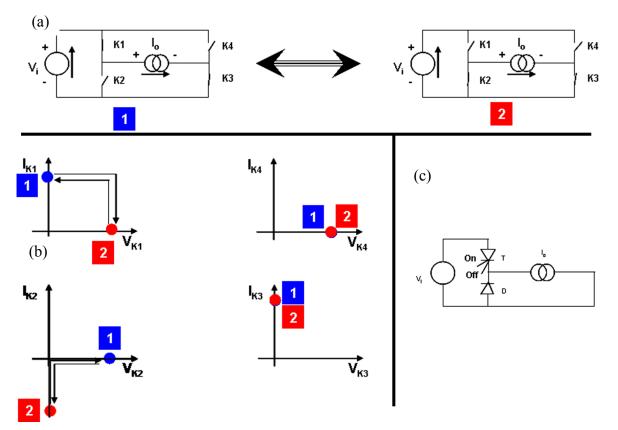

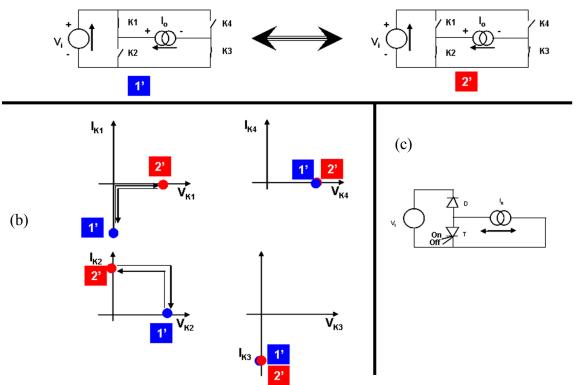

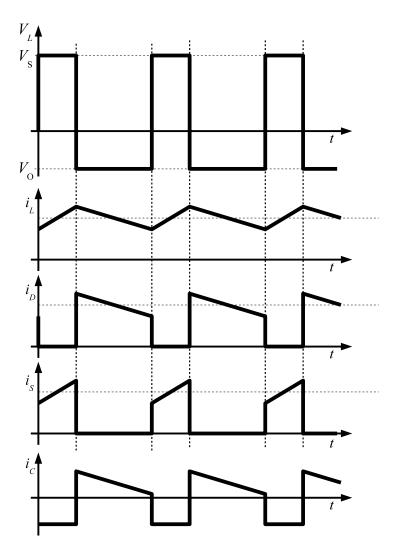

**Fig. 30:** Study of a non-reversible current chopper. (a) – sequences 1 and 2 (change in K1, K2, and K4); (b) – Current-voltage characteristics of each switch for the two sequences; (c) corresponding topology with transistor and diode.

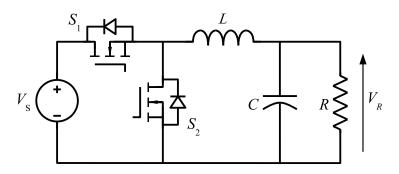

## 8.2.2 Reversible current chopper

Hypothesis:

- power conversion between a voltage source and a current source;

- the input voltage source is bidirectional in current;

- the output current source is unidirectional in voltage and bidirectional in current.

Following the steps of the synthesis method:

- 1. a direct converter topology can be used;

- 2. cell (2,6) of the general table according to the source reversibilities;

- 3. sequence 1 (active phase) and 2 (free wheel phase) of Figs. 30 and 31;

- 4. the different plots for the four switches are represented in Fig. 30 for the two sequences for the transfer of energy from the input source to the output source. Figure 31 represents the analysis of the brake phase: transfer of energy from the output source to the input source.

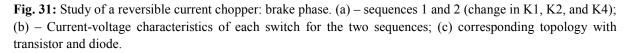

- 5. the analysis of the two phases leads to the determination of the structure presented in Fig. 32.

**DEFINITION OF POWER CONVERTERS**

Brake phase

Fig. 32: Structure of reversible current chopper

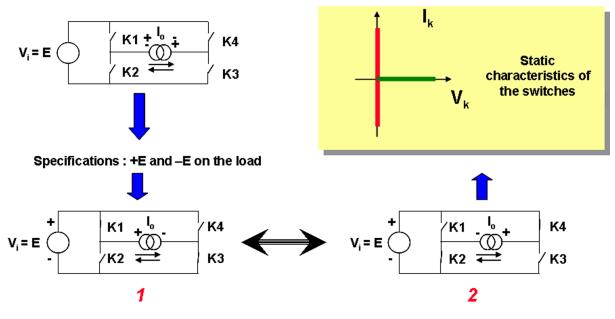

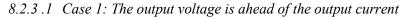

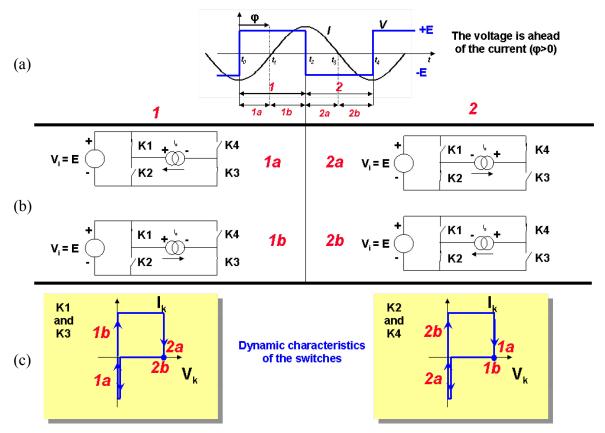

## 8.2.3 Voltage inverter

Hypothesis:

- power conversion between a voltage source and a current source;

- the input voltage source is unidirectional in voltage and bidirectional in current; it is a DC source of value *E*.

- the output current source is bidirectional in voltage and bidirectional in current; it is an AC source. The specification is to get a +E, -E voltage at the output of the converter.

The steps of the synthesis method are followed.

- 1. A direct converter topology can be used.

- 2. Cell (2,5) of the general table according to the source reversibilities.

- 3. The two sequences are shown in Fig. 33.

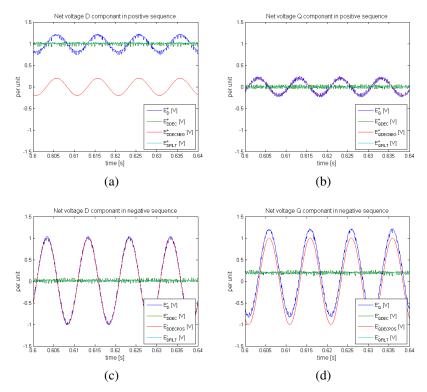

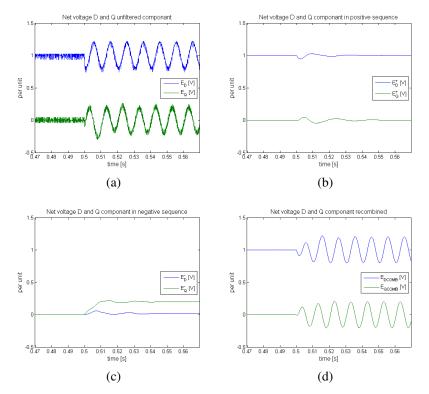

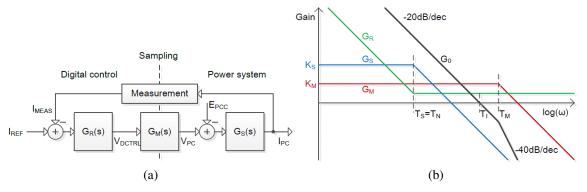

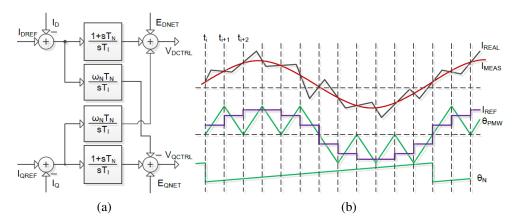

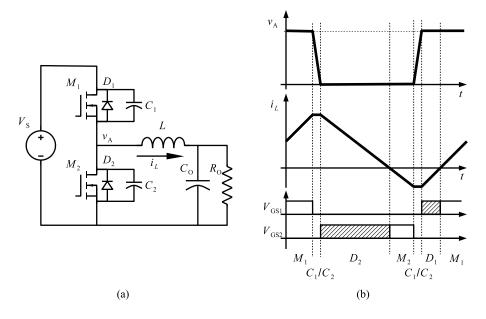

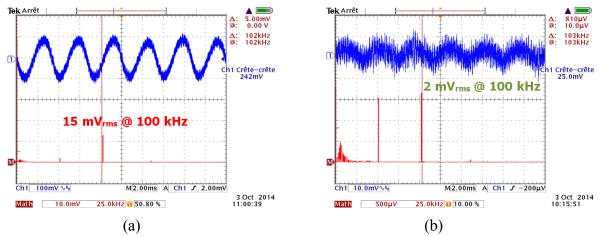

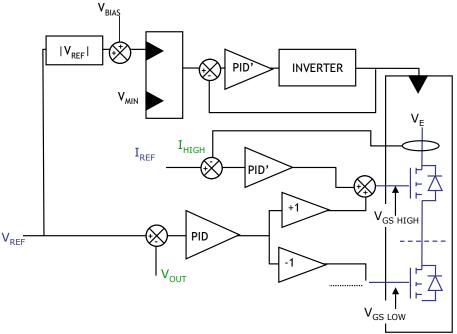

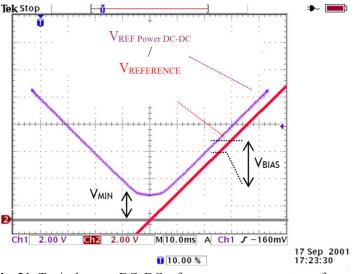

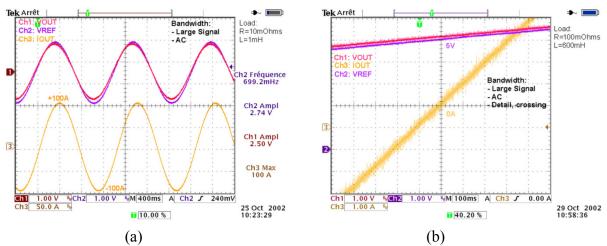

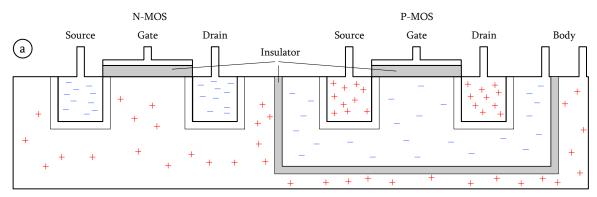

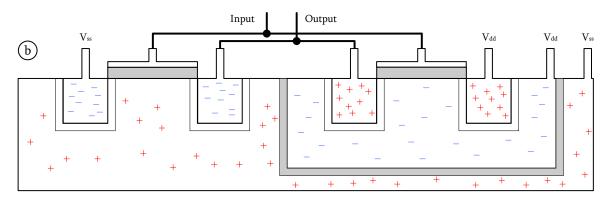

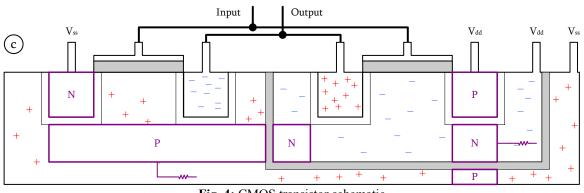

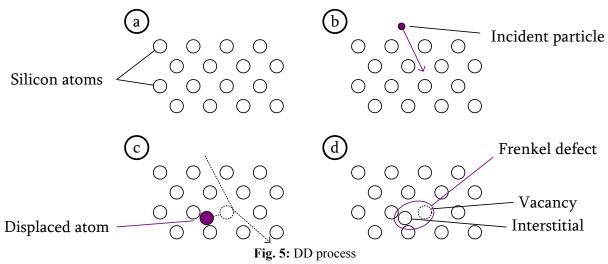

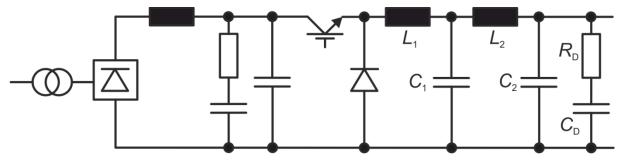

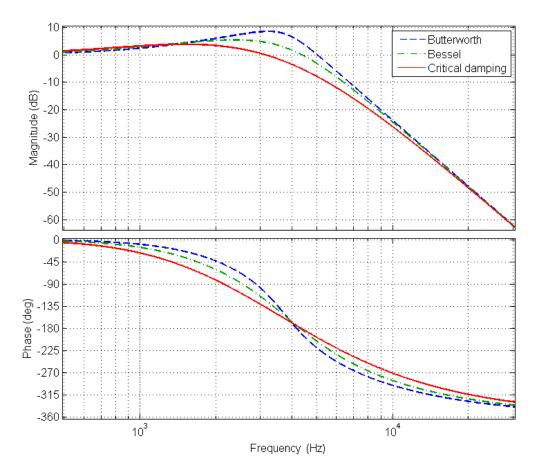

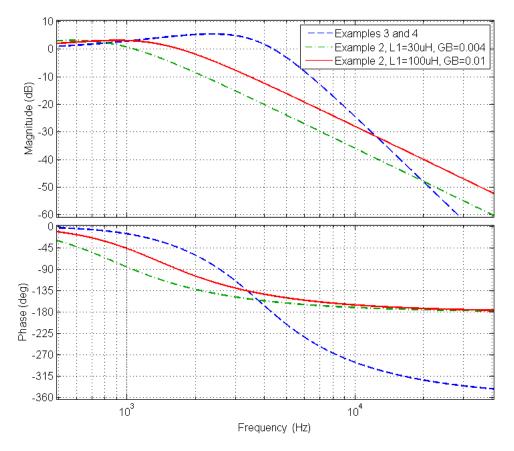

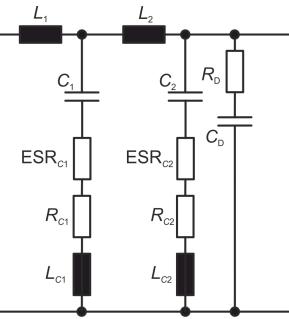

- 4. From the analysis of two sequences, it can be deduced that the switches must be bidirectional in current and unidirectional in voltage. They correspond to three-segment switches (D and T in parallel; Fig. 10).